# SD Specifications Part 1 UHS-II Simplified Addendum

Version 1.02 May 28, 2014

Addendum to: SD Specifications Part 1 Physical Layer Simplified Specification Version 4.10 January 22, 2013, or later

> Technical Committee SD Card Association

|  | Date             | Version | Changes compared to previous issue                                                            |

|--|------------------|---------|-----------------------------------------------------------------------------------------------|

|  | November 8, 2013 | 1.01    | The first release of UHS-II Simplified Addendum (Created by the UHS-II Addendum Version 1.01) |

|  | May 28, 2014     | 1.02    | Fixed Section number from 3.2 to 3.5                                                          |

### **Revision History**

To the extent this proposed specification, which is being submitted for review under the IP Policy, implements, incorporates by reference or refers to any portion of versions 1.0 or 1.01 of the SD Specifications (including Parts 1 through 4), adoption of the proposed specification shall require Members utilizing the adopted specification to obtain the appropriate licenses from the SD-3C, LLC, as required for the utilization of those portion(s) of versions 1.0 or 1.01 of the SD Specifications.

For example, implementation of the SD Specifications in a host device under versions 1.0 or 1.01 and under the adopted specification requires the execution of a SD Host Ancillary License Agreement with the SD-3C, LLC; and implementation of the SD Specifications under versions 1.0 or 1.01 and under the proposed specification in a SD Card containing any memory storage capability (other than for storage of executable code for a controller or microprocessor within the SD Card) requires the execution of a SD Memory Card License Agreement with the SD-3C, LLC.

# **Release of SD Simplified Specification/Addendum**

The following conditions apply to the release of the SD Simplified Specification/Addendum by the SD Card Association. The Simplified Specification/Addendum is a subset of the complete version of SD Specification/Addendum which is owned by the SD Card Association.

# **Conditions for publication**

#### Publisher and Copyright Holder:

SD Card Association 2400 Camino Ramon, Suite 375 San Ramon, CA 94583 USA Telephone: +1 (925) 275-6615, Fax: +1 (925) 886-4870 E-mail: office@sdcard.org

#### Notes:

This Simplified Specification/Addendum is provided on a non-confidential basis subject to the disclaimers below. Any implementation of the Simplified Specification/Addendum may require a license from the SD Card Association or other third parties.

#### **Disclaimers:**

The information contained in the Simplified Specification/Addendum is presented only as a standard specification/Addendum for SD Cards and SD Host/Ancillary products and is provided "AS-IS" without any representations or warranties of any kind. No responsibility is assumed by the SD Card Association for any damages, any infringements of patents or other right of the SD Card Association or any third parties, which may result from its use. No license is granted by implication, estoppel or otherwise under any patent or other rights of the SD Card Association or any third party. Nothing herein shall be construed as an obligation by the SD Card Association to disclose or distribute any technical information, know-how or other confidential information to any third party.

# **Conventions Used in This Document**

#### **Naming Conventions**

• Some terms are capitalized to distinguish their definition from their common English meaning. Words not capitalized have their common English meaning.

#### Numbers and Number Bases

- Hexadecimal numbers are written with a lower case "h" suffix, e.g., FFFFh and 80h.

- Binary numbers are written with a lower case "b" suffix (e.g., 10b).

- Binary numbers larger than four digits are written with a space dividing each group of four digits, as in 1000 0101 0010b.

- All other numbers are decimal.

#### Key Words

- May: Indicates flexibility of choice with no implied recommendation or requirement.

- Shall: Indicates a mandatory requirement. Designers shall implement such mandatory requirements to ensure interchangeability and to claim conformance with the specification.

- Should: Indicates a strong recommendation but not a mandatory requirement. Designers should give strong consideration to such recommendations, but there is still a choice in implementation.

#### **Application Notes**

Some sections of this document provide guidance to the host implementers as follows:

Application Note:

This is an example of an application note.

# **Table of Contents**

| 1. General                                                 | 1  |

|------------------------------------------------------------|----|

| 2. System Features                                         | 2  |

| 3. UHS-II System Concept                                   | 3  |

| 3.1 Interface Speed                                        |    |

| 3.2 Connection Topologies                                  |    |

| 3.2.1 Point to Point Connection                            |    |

| 3.2.2 Multi-device Connection                              | 5  |

| 3.2.2.1 Ring Connection                                    |    |

| 3.2.2.2 Hub Connection                                     |    |

| 3.3 Layering                                               |    |

| 3.4 UHS-II Transaction                                     |    |

| 3.4.1 UHS-II Packet                                        |    |

| 3.4.2 Data Transaction                                     |    |

| 3.4.3 CM-TRAN                                              |    |

| 3.4.5 Aborting Transaction                                 |    |

| 3.5 UHS-II Initialization Outline                          |    |

| 3.5.1 UHS-II Initialization Flow without Boot Code Loading |    |

| 3.5.2 UHS-II Initialization Flow with Boot Code Loading    |    |

|                                                            |    |

| 4. Physical Layer Specification                            | 14 |

| 4.1 Physical Layer Overview                                |    |

| 4.2 Physical Layer Interface Architecture                  |    |

| 4.2.1 Lane Definition                                      |    |

| 4.2.2 Range Definition for Data Rate                       |    |

| 4.2.3 Power Supply Connections                             |    |

| 4.3 Electrical Specification                               |    |

| 4.3.1 Definition of Single-ended and Differential Signals  |    |

| 4.3.2 Specification of Transmitter and Receiver            |    |

| 4.3.3 Eye-mask Template                                    |    |

| 4.3.4 Jitter                                               |    |

| 4.3.5 Return Loss                                          |    |

| 4.4 EIDL State                                             |    |

| 4.5 Symbol Coding<br>4.6 Loopback Mode                     |    |

| 4.6 LOOPDack Mode                                          |    |

| 4.7.1 The Sequences used in PHY Test Mode                  |    |

| 4.7.2 Definition of TMD1 and TMD2                          |    |

| 4.7.2 Definition of TMDT and TMD2                          |    |

| 4.7.2.2 TMD2                                               | -  |

| 4.7.3 Test Modes                                           |    |

| 4.7.4 An Example Procedure                                 |    |

| 4.7.5 Test Mode for Host                                   |    |

|                                                            |    |

| 5. Link Layer Specification                                |    |

| 5.1 Link Layer Overview                           | 33 |

|---------------------------------------------------|----|

| 5.2 Link Layer Protocol                           | 33 |

| 5.2.1 Protocol Overview                           | 33 |

| 5.2.2 Link Symbol Set (LSS)                       | 33 |

| 5.2.3 Header for UHS-II Packet                    |    |

| 5.2.4 Message Packet (MSG)                        | 35 |

| 5.2.4.1 Overview                                  | 35 |

| 5.2.4.2 CODE Definition for Each IDX              | 36 |

| 5.2.4.3 MSG Duplication                           |    |

| 5.2.5 Error Identifier                            |    |

| 5.2.6 Framing Rules                               |    |

| 5.2.7 Symbol Encoding and Byte Ordering in 8b/10b |    |

| 5.2.8 Physical Lane State Machine (PLSM)          |    |

| 5.2.8.1 Overview                                  |    |

| 5.2.9 Data Link State Machine (DLSM)              |    |

| 5.2.9.1 Overview                                  | 39 |

|                                                   |    |

| 6. Transaction Layer Specification                |    |

| 6.1 Transaction Layer Overview                    |    |

| 6.1.1 Packet Types and Format Overview            |    |

| 6.2 Transaction Layer Protocol                    |    |

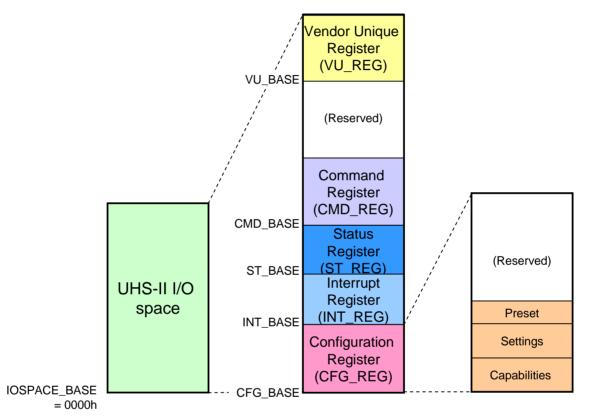

| 6.2.1 UHS-II I/O Space and Memory Address Space   |    |

| 6.2.2 Packet Format Details                       |    |

| 6.2.2.1 Header                                    |    |

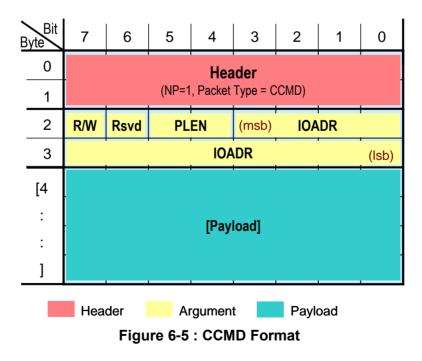

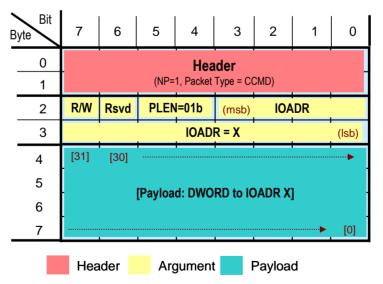

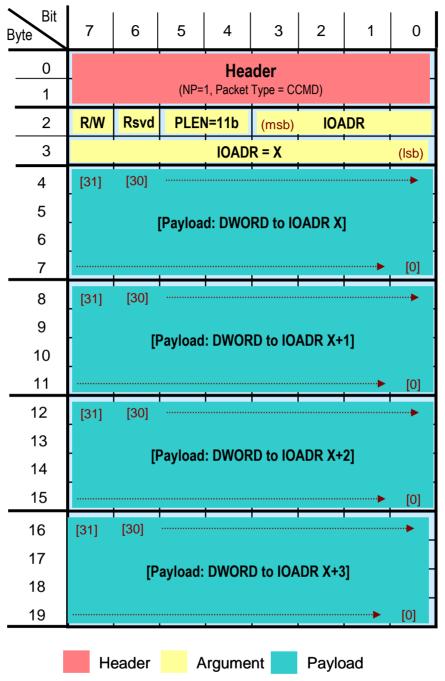

| 6.2.2.2 CCMD                                      |    |

| 6.2.2.3 Broadcast CCMD                            |    |

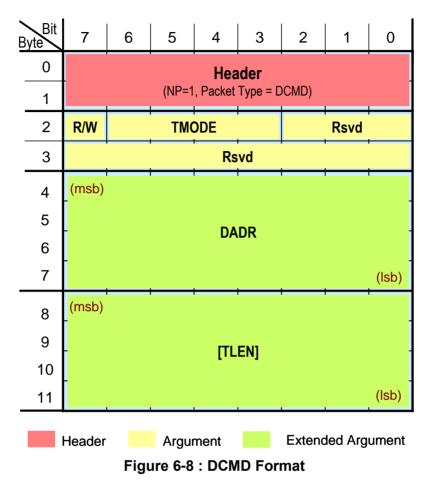

| 6.2.2.4 DCMD                                      |    |

| 6.2.2.5 RES (NACK = 0)                            |    |

| 6.2.2.6 RES (NACK = 1)<br>6.2.2.7 DATA            |    |

| 6.2.2.8 Operation of Reserved Bits in the Packet  |    |

| 6.2.3 Supplements of UHS-II Initialization        |    |

| 6.2.4 Transition to Dormant State                 |    |

| 6.2.4.1 General                                   |    |

| 6.2.4.2 Hibernate Mode                            |    |

| 6.2.4.2.1 Overview                                | -  |

| 6.2.5 Reset                                       |    |

| 6.2.6 Device Initialization Mechanism             |    |

| 6.2.6.1 General                                   |    |

| 6.2.7 Enumeration Mechanism                       |    |

| 6.2.7.1 General                                   |    |

| 6.2.8 Configuration Mechanism                     |    |

| 6.2.8.1 Basic Specification                       |    |

| 6.2.8.2 Determination of Block Length             |    |

| 6.2.8.3 Quick Configuration                       | 61 |

| 6.2.9 Configuration Register (CFG_REG)            | 63 |

| 6.2.9.1 Register Map                              |    |

| 6.2.9.2 CFG_REG Description                       |    |

| 6.2.9.2.1 Generic Capabilities Register           |    |

| 6.2.9.2.2 PHY Capabilities Register               |    |

| 6.2.9.2.3 LINK/TRAN Capabilities Register         | 67 |

| 6.2.9.2.4 Generic Settings Register                                 |     |

|---------------------------------------------------------------------|-----|

| 6.2.9.2.5 PHY Settings Register                                     |     |

| 6.2.9.2.6 LINK/TRAN Settings Register                               | 71  |

| 6.2.9.2.7 Preset Register                                           |     |

| 6.2.10 Status Register (ST_REG)                                     |     |

| 6.2.10.1 Register Map                                               |     |

| 6.2.10.2 ST_REG Description                                         |     |

| 6.2.10.2.1 Status in TRANS_ABORT Register                           |     |

| 6.2.11 Interrupt Register (INT_REG)                                 |     |

| 6.2.11.1 Register Map                                               |     |

| 6.2.11.2 INT_REG Description                                        |     |

| 6.2.11.2.1 INT Enable                                               |     |

| 6.2.11.2.2 INT Status                                               |     |

| 6.2.12 Command Register (CMD_REG)                                   |     |

| 7. SD-TRAN Specification                                            | 76  |

| 7.1 SD-TRAN Overview                                                |     |

| 7.1.1 Packet Types and Format Overview                              | 76  |

| 7.1.2 Registers for Legacy SD                                       | 77  |

| 7.2 SD-TRAN Protocol                                                | 77  |

| 7.2.1 Packet Format Details                                         | 77  |

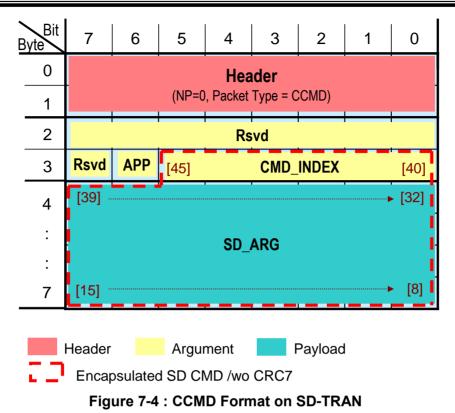

| 7.2.1.1 CCMD                                                        |     |

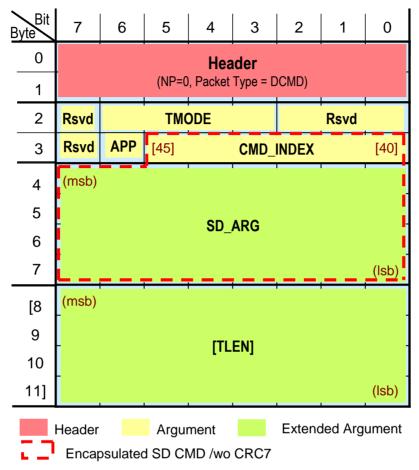

| 7.2.1.2 DCMD                                                        | 79  |

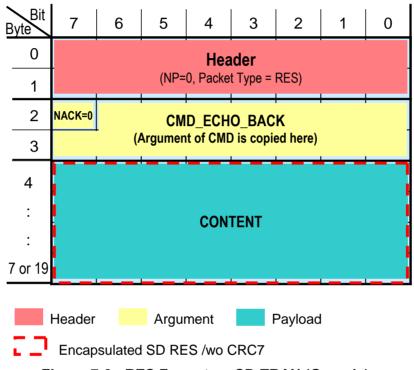

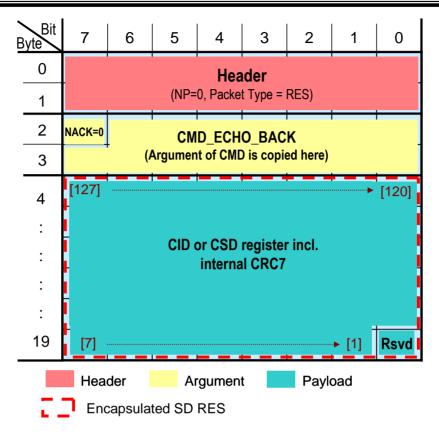

| 7.2.1.3 RES                                                         |     |

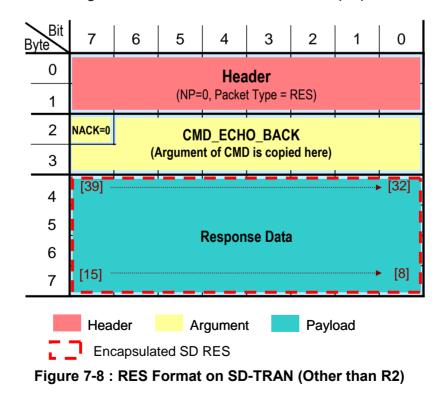

| 7.2.1.4 RES (NACK = 1)                                              |     |

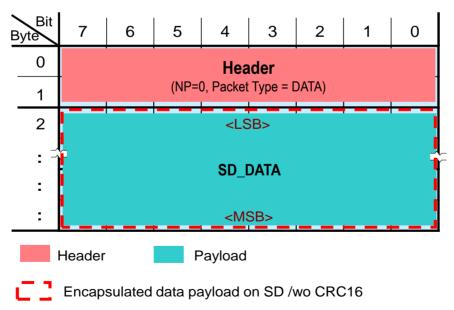

| 7.2.1.5 DATA                                                        |     |

| 7.2.2 DATA Burst Framing Rules in SD-TRAN                           | 83  |

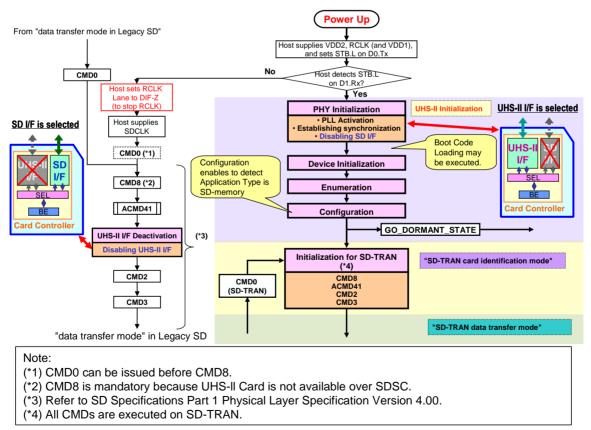

| 7.2.3 Interface Selection for UHS-II Card and Initialization        |     |

| 7.2.3.1 Overview                                                    |     |

| 7.2.3.2 Interface Selection after Power Up                          |     |

| 7.2.3.3 Interface Selection after FULL_RESET or GO_DORMANT_STATE    |     |

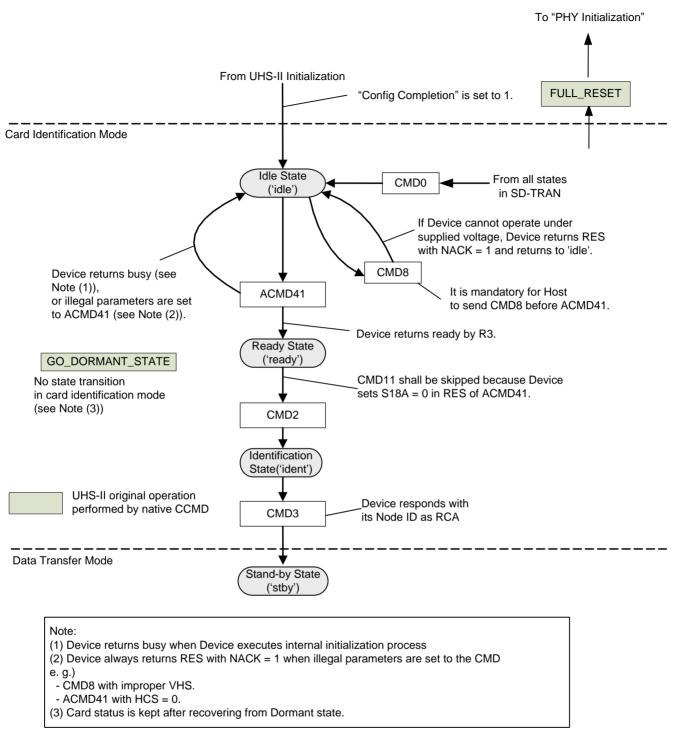

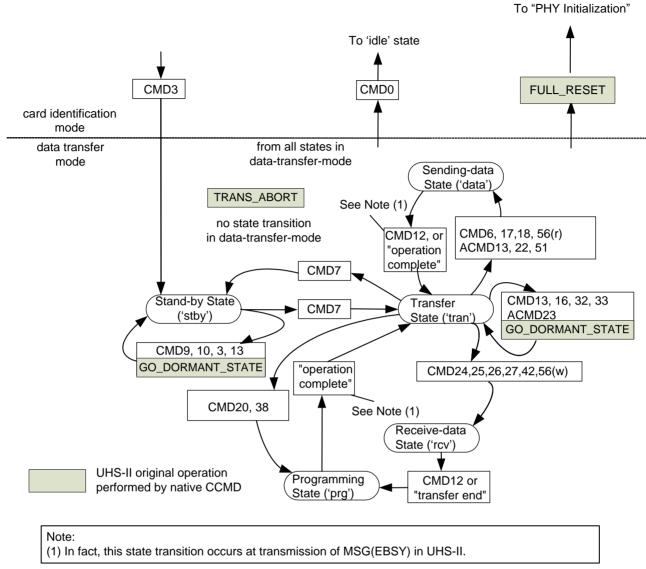

| 7.2.4 Transaction Control and Management State Machine              | 85  |

| 7.2.4.1 Card Identification Mode                                    |     |

| 7.2.4.2 Data Transfer Mode                                          | 87  |

| 8. 2L-HD Mode (optional)                                            | 89  |

| 8.1 Overview                                                        | 89  |

| 9. Additional Lanes Support (optional)                              | 90  |

| 9.1 Overview                                                        |     |

| Annough A (Normative) - Defenses                                    | • • |

| Appendix A (Normative) : Reference                                  |     |

| A.1 Related Documentation                                           |     |

| Appendix B (Normative) : Special Terms                              | 92  |

| B.1 Terminology                                                     |     |

| B.2 Abbreviations                                                   |     |

| Appendix C (Normative) : Test Condition of Measuring Output Signals | 90  |

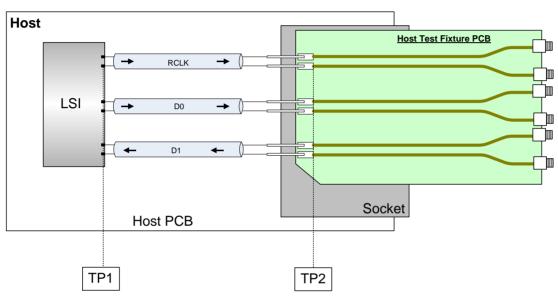

| C.1 Test Condition for Host Output Signal at TP2                    |     |

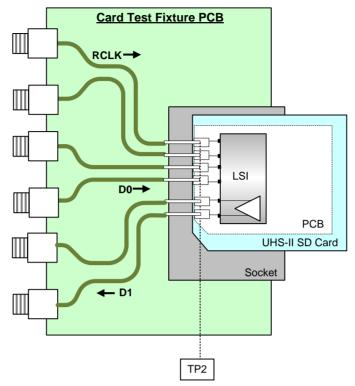

| C.2 Test Condition for Card Output Signal at TP2                    |     |

|                                                                     |     |

| Appendix D (Normative) : Register                                |     |

|------------------------------------------------------------------|-----|

| D.1 Register Summary                                             |     |

| D.1.1 Register Types                                             |     |

| D.1.2 Register Initial Values                                    |     |

| ·                                                                |     |

| Appendix E (Informative) : Design Guide                          | 99  |

| Appendix F (Informative) : PHY-LINK I/F                          | 100 |

| Appendix G (Informative) : Host's Operation in Detecting Timeout | 101 |

# Table of Figures

| Figure 3-1 : Interface Speed Comparison                                                |      |

|----------------------------------------------------------------------------------------|------|

| Figure 3-2 : Point to Point Topology (FD mode)                                         |      |

| Figure 3-3 : Point to Point Topology (Supporting 2L-HD Mode)                           |      |

| Figure 3-4 : Direction Changing in 2L-HD Mode                                          |      |

| Figure 3-5 : Example of Ring Connection                                                |      |

| Figure 3-6 : Examples of RCLK distribution method for Ring                             |      |

| Figure 3-7 : Example of Hub Connection                                                 | 7    |

| Figure 3-8 : Layering Overview                                                         | 7    |

| Figure 3-9 : Basic UHS-II Transaction                                                  | 9    |

| Figure 3-10 : UHS-II Transaction by SD-TRAN                                            | . 10 |

| Figure 3-11 : UHS-II Initialization Flow                                               |      |

| Figure 3-12 : UHS-II Initialization Flow When Boot Code Loading Is Executed            | . 13 |

| Figure 4-1: Physical Layer Overview                                                    | . 14 |

| Figure 4-2: Physical Layer Interface Architecture                                      | . 15 |

| Figure 4-3: Signal Test Points                                                         | . 16 |

| Figure 4-4: Single-ended Signal Names on Differential Line                             | . 17 |

| Figure 4-5: Definition of Single-ended and Differential Signals                        |      |

| Figure 4-6: Eye-mask Templates                                                         |      |

| Figure 4-7: Jitter Tolerance Specification                                             | . 19 |

| Figure 4-8: Differential Mode Return Loss (RL <sub>DD</sub> ) Template for Device      |      |

| Figure 4-9: Differential Mode Return Loss (RL <sub>DD</sub> ) Template for Host        |      |

| Figure 4-10: Common-mode Return Loss (RL <sub>cc</sub> ) Template                      |      |

| Figure 4-11: Common-to-Differential Return Loss (RLpc) Template                        |      |

| Figure 4-12: Power Delivery Network for VDD1 and VDD2 Domains                          |      |

| Figure 4-13: Line States and Timing in the Recovery from EIDL State and in EIDL Entry  |      |

| Figure 4-14: Diagram of Symbol Coding                                                  |      |

| Figure 4-15: Location of Forward Loopback in PHY of the Host                           |      |

| Figure 4-16: Location of Backward Loopback in PHY of the Host                          |      |

| Figure 4-17: Location of Forward Loopback in PHY of the Device                         |      |

| Figure 4-18: Location of Backward Loopback in PHY of the Device                        |      |

| Figure 4-19: Sequences used in PHY Test Mode                                           | . 25 |

| Figure 4-20: Structure of TMD1 and TMD2                                                | . 27 |

| Figure 4-21: Normal Modes Sequence                                                     | . 29 |

| Figure 4-22: Disconnect Mode Sequence                                                  |      |

| Figure 4-23: An Example Procedure (Backward Loop Back Test with PLL Multiplier is x30) | . 31 |

| Figure 4-24: States Regarding Host PHY Test                                            | . 32 |

| Figure 5-1 : Link Layer Overview                                                       |      |

| Figure 5-2 : Header Format                                                             |      |

| Figure 5-3 : MSG Format                                                                |      |

| Figure 5-4 : Packet Framing Rule of TLP                                                |      |

| Figure 5-5 : Packet Framing Rule of MSG                                                |      |

| Figure 5-6 : DATA Burst Framing Rule in Block Mode (N_FCU = 2)                         |      |

| Figure 5-7 : Framing Rules for Fractional DATA Burst                                   |      |

| Figure 5-8 : Framed DATA Packet Format in Case of Block Length Is Odd                  |      |

| Figure 5-9 : DATA Burst Framing Rule in Byte Mode                                      |      |

| Figure 5-10 : DATA Burst Framing Rule in Byte Mode When TLEN Is Odd                    |      |

| Figure 5-11 : Symbol Encoding                                                          |      |

| Figure 5-12 : Byte Ordering in Symbol Transfer                                         |      |

| Figure 5-13 : Physical Lane State Machine (PLSM)                                       |      |

|                                                                                        |      |

| Figure 5-14 : VLD State                                                                      |    |

|----------------------------------------------------------------------------------------------|----|

| Figure 5-15 : Data Link State Machine (DLSM)                                                 |    |

| Figure 6-1 : Transaction Layer Overview                                                      |    |

| Figure 6-2 : TLP Format Overview                                                             |    |

| Figure 6-3 : Control Transaction and Data Transaction Sequence                               |    |

| Figure 6-4 : UHS-II I/O Space Layout for Device                                              |    |

| Figure 6-5 : CCMD Format.                                                                    |    |

| Figure 6-6 : Transmission Order of Payload in CCMD (PLEN = 01b)                              |    |

| Figure 6-7 : Transmission Order of Payload in CCMD (PLEN = 11b)                              |    |

| Figure 6-8 : DCMD Format                                                                     |    |

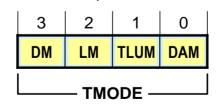

| Figure 6-9 : TMODE Parameters                                                                |    |

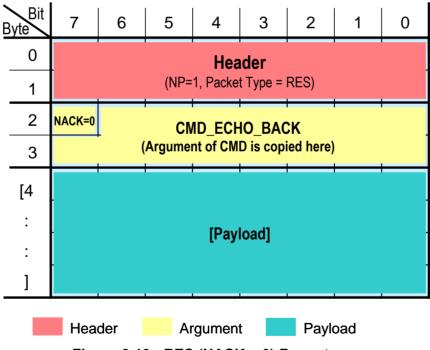

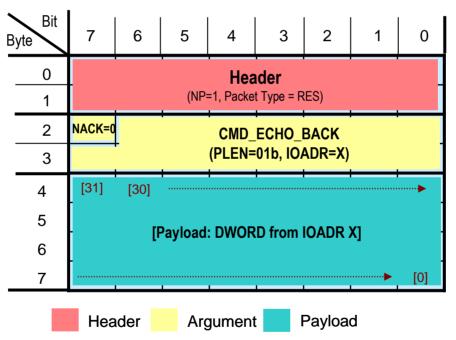

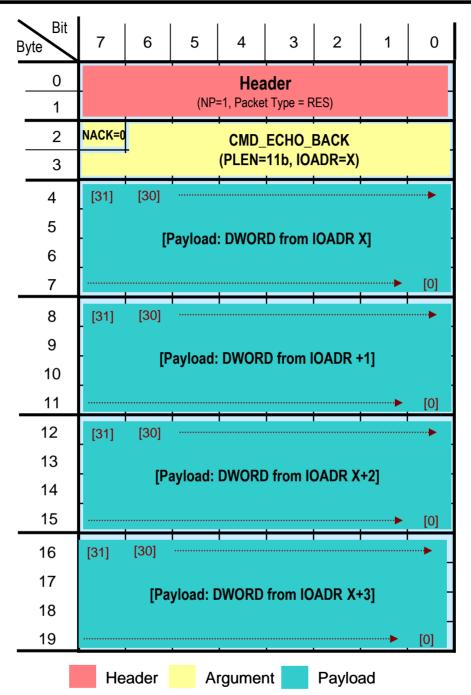

| Figure 6-10 : RES (NACK = 0) Format                                                          |    |

| Figure 6-11 : Transmission Order of Payload in RES (NACK = 0, PLEN = 01b)                    |    |

| Figure 6-12 : Transmission Order of Payload in RES (NACK = 0, PLEN = 11b)                    |    |

| Figure 6-13 : RES (NACK = 1) Format                                                          |    |

| Figure 6-14 : Basic DATA Format                                                              |    |

| Figure 6-15 : UHS-II Initialization Flow When Recovery from Dormant State                    |    |

| Figure 6-16 : An Example of UHS-II Initialization Flow (in Case of Using Higher Speed Range) |    |

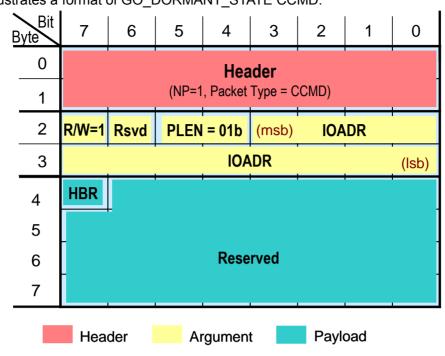

| Figure 6-17 : GO_DORMANT_STATE CCMD Format                                                   |    |

| Figure 6-18 : Transition from / to Hibernate Mode                                            |    |

| Figure 6-19 : Entry to Hibernate Mode                                                        |    |

| Figure 6-20 : Exit from Hibernate Mode                                                       |    |

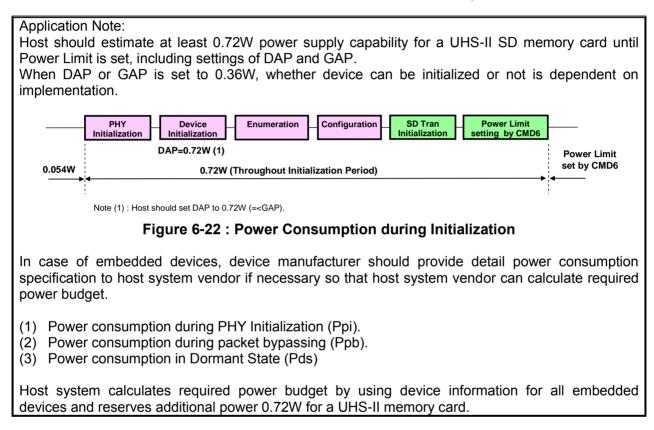

| Figure 6-21 : DEVICE_INIT CCMD Format                                                        |    |

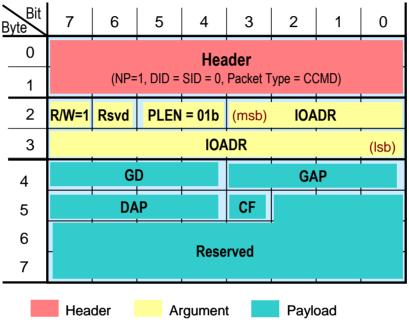

| Figure 6-22 : Power Consumption during Initialization                                        | 59 |

| Figure 6-23 : Device's Operation Flow of Receiving DEVICE_INIT                               | 59 |

| Figure 6-24 : DEVICE_INIT Broadcast CCMD Issued by Host                                      |    |

| Figure 6-25 : Host's Operation Flow of Receiving DEVICE_INIT                                 | 59 |

| Figure 6-26 : Device Initialization Process (Example 1)                                      | 59 |

| Figure 6-27 : Device Initialization Process (Example 2)                                      | 59 |

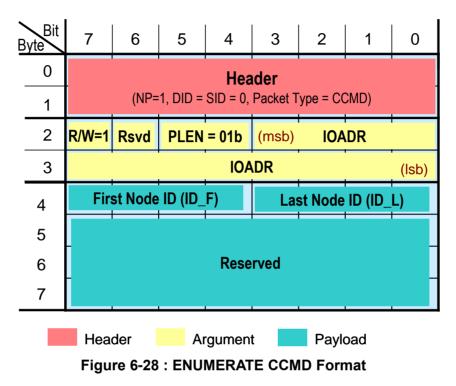

| Figure 6-28 : ENUMERATE CCMD Format                                                          | 60 |

| Figure 6-29 : Device's Algorithm for Enumeration Process                                     | 60 |

| Figure 6-30 : Enumeration Process in Point to Point Connection (Example 1)                   |    |

| Figure 6-31 : Enumeration Process in Point to Point Connection (Example 2)                   | 60 |

| Figure 6-32 : Enumeration Process in Ring Connection (Example 1)                             |    |

| Figure 6-33 : Enumeration Process in Ring Connection (Example 2)                             |    |

| Figure 6-34 : Device Configuration Flow                                                      |    |

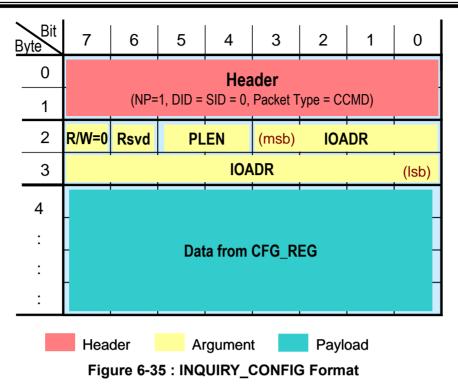

| Figure 6-35 : INQUIRY_CONFIG Format                                                          | 62 |

| Figure 6-36 : Operation of INQUIRY_CONFIG                                                    | 62 |

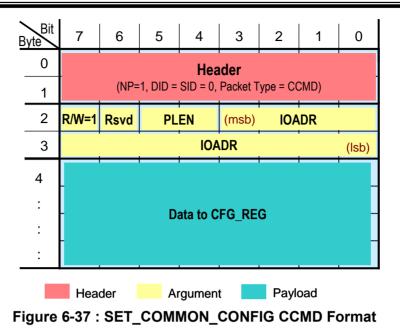

| Figure 6-37 : SET_COMMON_CONFIG CCMD Format                                                  | 63 |

| Figure 7-1 : SD-TRAN Overview                                                                |    |

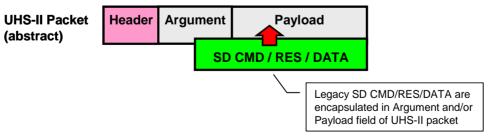

| Figure 7-2 : Conceptual Diagram of SD-encapsulation                                          |    |

| Figure 7-3 : Encapsulation of Legacy SD Format                                               |    |

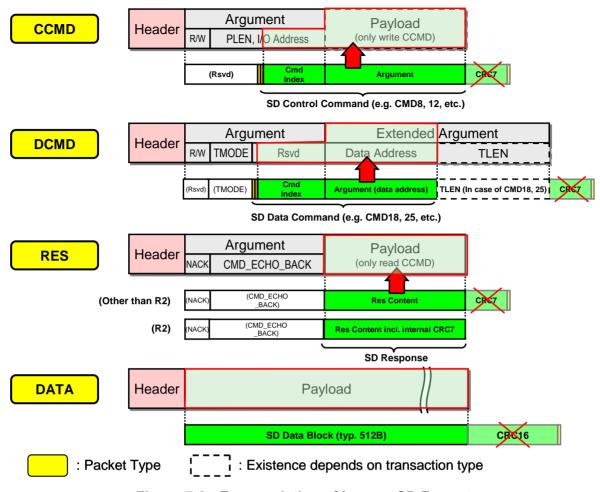

| Figure 7-4 : CCMD Format on SD-TRAN                                                          |    |

| Figure 7-5 : DCMD Format on SD-TRAN                                                          |    |

| Figure 7-6 : RES Format on SD-TRAN (Generic)                                                 |    |

| Figure 7-7 : RES Format on SD-TRAN (R2)                                                      |    |

| Figure 7-8 : RES Format on SD-TRAN (Other than R2)                                           | 81 |

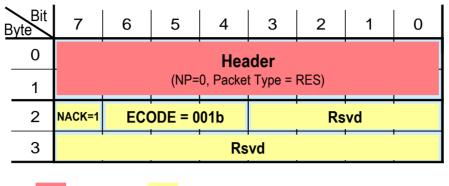

| Figure 7-9 : RES (NACK = 1) Format on SD-TRAN                                                |    |

| Figure 7-10 : DATA Format on SD-TRAN                                                         |    |

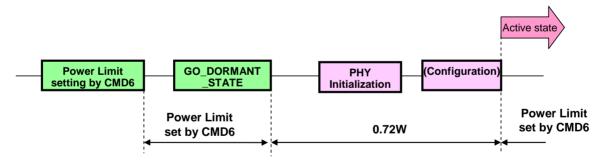

| Figure 7-11 : Initialization Flow after Power Up                                             |    |

| Figure 7-12 : Initialization Flow after FULL_RESET or GO_DORMANT_STATE                       |    |

| Figure 7-13 : Power Consumption after Exiting from Dormant State                             |    |

| Figure 7-14 : State Diagram on SD-TRAN (Card Identification Mode)                            |    |

| ······································                                                       |    |

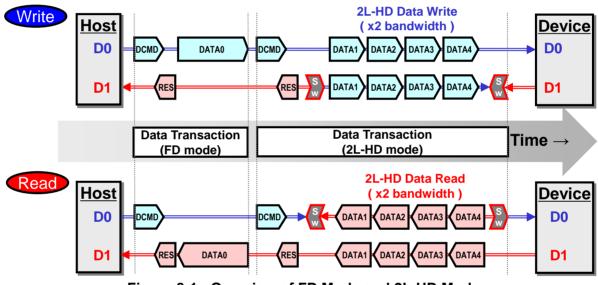

| Figure 7-15 : State Diagram on SD-TRAN (Data Transfer Mode)<br>Figure 8-1 : Overview of FD Mode and 2L-HD Mode         |  |

|------------------------------------------------------------------------------------------------------------------------|--|

| Figure 9-1 : Possible Lanes Configurations in FD / 2L-HD Mode<br>Figure C- 1: Host Test Fixture Illustration (Concept) |  |

| Figure C- 2: Card Test Fixture Illustration (Concept)                                                                  |  |

# **Table of Tables**

| Table 3-1 : Definition of Initiator                           | 8    |

|---------------------------------------------------------------|------|

| Table 4-1: Range Definition for Data Rate                     | . 16 |

| Table 5-1 : Special Symbols for Link Layer                    |      |

| Table 5-2:Link Symbol Set                                     | . 33 |

| Table 5-3 : Packet Type Encodings and Descriptions            | . 34 |

| Table 5-4 : Detailed Definition of MSG                        | . 35 |

| Table 5-5 : Code Definition of FCREQ and FCRDY                | . 36 |

| Table 5-6 : Code Definition of STAT                           |      |

| Table 5-7 : PLSM State Definition for Tx and Rx               |      |

| Table 6-1 : I/O Address Space Map                             | .44  |

| Table 6-2 : Definition of PLEN                                |      |

| Table 6-3 : Availability of TMODE                             | . 50 |

| Table 6-4 : Error Categories and Descriptions                 | . 53 |

| Table 6-5 : Operation for the Reserved Bits in the Packet     | . 54 |

| Table 6-6 : CFG_REG Map                                       | . 64 |

| Table 6-7 : Generic Capabilities Register                     |      |

| Table 6-8 : PHY Capabilities Register                         |      |

| Table 6-9 : LINK/TRAN Capabilities Register                   |      |

| Table 6-10 : Generic Settings Register                        |      |

| Table 6-11 : PHY Settings Register                            |      |

| Table 6-12 : Detailed Definitions of Transmission Speed Range |      |

| Table 6-13 : LINK/TRAN Settings Register                      |      |

| Table 6-14 : Preset Register                                  | .72  |

| Table 6-15 : Status Register                                  | .72  |

| Table 6-16 : Status in TRANS_ABORT Register                   |      |

| Table 6-17 : Interrupt Register                               |      |

| Table 6-18 : INT Enable Register                              |      |

| Table 6-19 : INT Status Register                              |      |

| Table 6-20 : Command Register                                 | .75  |

|                                                               |      |

| Table D- 1 : Register Attribute Table                         | . 98 |

# 1. General

This Simplified Addendum defines an additional category to the Part 1 Physical Layer Simplified Specification Version 4.10. The following sections describe additional and modified parts of the base specification for this new category.

Key background factors behind Ultra High Speed Type II (UHS-II) Specification are shown below:

• High speed interface is required to handle large volumes of HD (High Definition) contents In recent years, the number of SD-applications which handle large amount of data is increasing steadily with an increase in HD (High Definition) contents (HD, Super-HD, 3D-TV, etc.). At the same time, the data size of HD contents is also increasing year by year. UHS-II is necessary to meet the ultrahigh-speed requirement to handle HD contents and farther large-capacity contents in the future.

# Interface should be widely available for many kinds of hosts It is difficult to keep signal integrity at high speed data transfer especially

It is difficult to keep signal integrity at high-speed data transfer especially for mobile devices. Generally, board design of hosts becomes more difficult with high speed interface. UHS-II should be considered both high-speed and availability for many kinds of hosts.

- Reusability of legacy resource (IPs, software, etc.) is important for host development Hosts require the compatibility with legacy protocol for their efficient development. For example, in SD protocol, preserving the SD legacy infrastructures (CMD, RES, States, Status, Errors, etc.) provides efficient development with SD hosts, and this leads to a speedy expansion of UHS-II applications.

- Interoperability and compatibility to Legacy SD I/F is important to avoid market confusion Hosts and Devices require also the interoperability and compatibility with Legacy SD cards installed based to enable UHS-II specifications to be smoothly adopted by the market.

- Low voltage, low power consumption and low EMI are needed for mobile devices To apply new high-speed interface to many kinds of mobile devices, it is important to realize low power consumption and low EMI. Some low power and low EMI techniques need to be considered for UHS-II.

- Multiple device connectivity for minimizing the number of ports and circuit size is required Multi device connectivity is required to reduce the number of ports and circuit size for lower developing cost.

System features of UHS-II Specification based on the background are described in the next chapter.

# 2. System Features

From background factors mentioned in Chapter 1, the features of UHS-II are defined as follows:

- (1) High speed interface up to 312MB/s

- (2) Easy implementation for whole system

- (3) Compatibility with Legacy SD interface

- (4) Ensuring effective performance of data transfer

- (5) Low voltage, low power consumption, low EMI

- (6) Multiple device connectivity

The followings are additional explanations for system features.

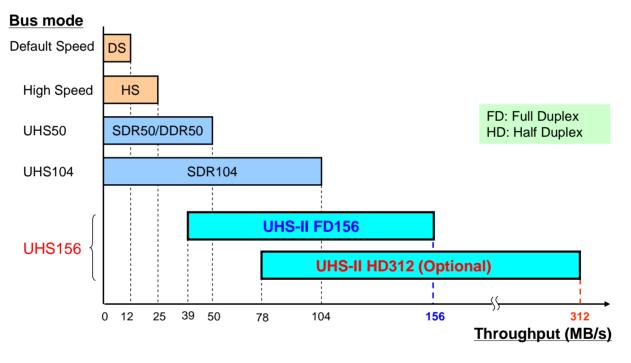

- Interface speed

- (1) Full Duplex mode (abbreviated to "FD mode"): data rate from 39MB/sec to 156MB/sec in the specifications and up to double the throughput in the future.

- (2) Half Duplex with 2 Lanes mode (abbreviated to "2L-HD mode"): data rate from 78MB/sec to 312MB/sec in the specifications and up to double the throughput in the future.

- (3) Interface speed is continuously variable.

- (4) Infrastructure for additional Lanes is defined as follows, allowing future bit rate expansion. (Refer to Section 3.1 for the definition of downstream or upstream.)

- Full Duplex with 2 Downstream and 1 Upstream Lanes mode (abbreviated to "2D1U-FD mode")

- Full Duplex with 1 Downstream and 2 Upstream Lanes mode (abbreviated to "1D2U-FD mode")

- Full Duplex with 2 Downstream and 2 Upstream Lanes mode (abbreviated to "2D2U-FD mode")

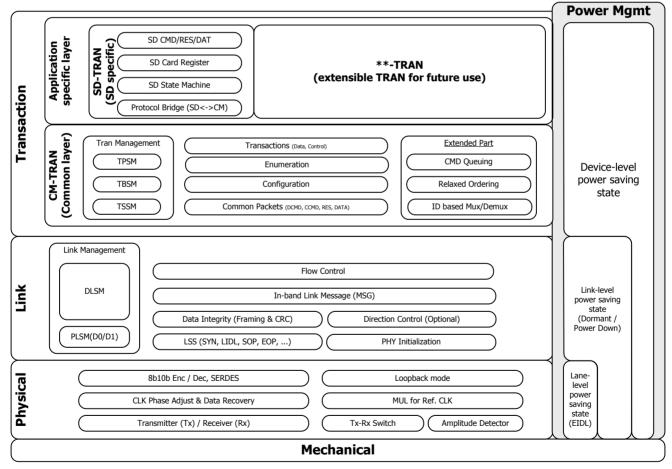

- Layering architecture

- (1) The system is divided into at least 4 layers, Mechanical, Physical, Link and Transaction.

- (2) Application specific layer can be introduced as a bridge between UHS-II common Transaction layer and the application.

- Legacy SD compatibility (for Card form factor)

- (1) Host and Device shall support Legacy SD I/F for ensuring fully backward compatibility.

- (2) Encapsulation of Legacy SD Format for Software Compatibility.

- Easy expansion for advanced features in the future

- (1) CMD Queuing: Another arbitrary command can be issued during some transaction.

- (2) Relaxed Ordering: Transaction order can be rearranged with reference to priority or processing speed.

- (3) Inter-device Communication: Some Device (called "CMD issuable Device") allows issuing commands and directly communicating to other Device.

# 3. UHS-II System Concept

In this chapter, the overall of UHS-II interface and system are described. UHS-II Card (or simply Card) denotes an SD memory card which supports UHS-II interface.

#### 3.1 Interface Speed

UHS-II interface consists of at least two Lanes based on two differential signaling lines. Each Lane provides up to 156MB/sec.

Basically, direction of both Lanes is opposite each other, that is, one is from Host to Device (downstream) and the other is from Device to Host (upstream). This mode is defined as Full Duplex mode (abbreviated to "FD mode").

It is possible that both Lanes are set to transfer data in the same directions. In that case, overall interface speed is doubled up to 312MB/sec (twice as high as FD mode). This status is defined as Half Duplex with 2 Lanes mode (abbreviated to "2L-HD mode") and is optional in this specification. It is also possible to have more than two Lanes, 3 or 4 Lanes for increasing system speed. This behavior is optional in this specification.

Figure 3-1 illustrates interface speed comparison among bus modes in Legacy SD, UHS-I and UHS-II (for UHS-II interface of 2 Lanes is assumed).

Figure 3-1 : Interface Speed Comparison

The interface speed shall be variable continuously.

### **3.2 Connection Topologies**

#### 3.2.1 Point to Point Connection

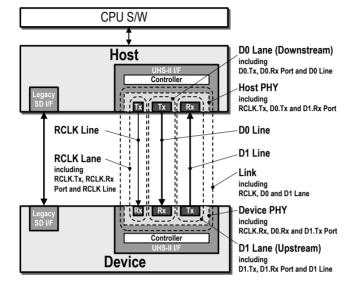

Minimum topology is consisting one Host and one Device is called "Point to Point" connection. Figure 3-2 shows the connection of a Host and a Device.

Figure 3-2 : Point to Point Topology (FD mode)

In UHS-II interface, both Host and Device have a PHY and a Controller which are responsible for performing Physical and Link / Transaction layer functions respectively. And UHS-II interface are connected by the following three Lanes.

- **RCLK:** transmits reference clock to Device from Host.

- **D0:** is a data Lane. It transmits commands, data, or other packets from Host to Device (downstream).

- **D1:** is another data Lane. It transmits responses, data, or other packets from Device to Host (upstream).

In general, each Lane consists of a Tx (Transmitter) Port and an Rx (Receiver) Port and a transmission Line between them. The notations used in this specification are used to specify each Tx or Rx Port clearly. For instance, Tx Port of RCLK Lane is described as RCLK.Tx and Rx Port of RCLK Lane is described as RCLK.Rx. The same rule is applied for other Lanes. And all Lanes are collectively called Link. Host PHY (PHY of Host) includes RCLK.Tx, D0.Tx and D1.Rx. Similarly, Device PHY (PHY of Device) includes RCLK.Rx, D0.Rx and D1.Tx.

All following descriptions relate to interface with two data Lanes. The optional case of 3 or 4 Lanes is described in Chapter 9.

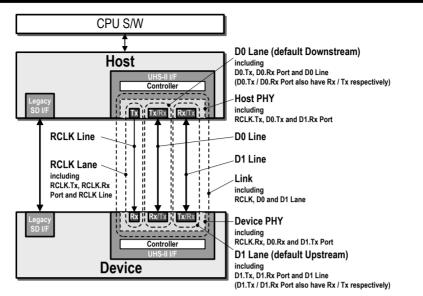

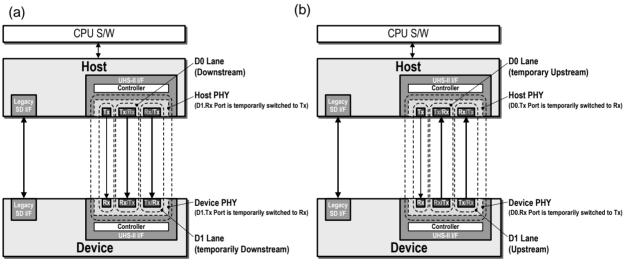

Figure 3-3 shows the connection of Host and Device supporting 2L-HD mode.

#### UHS-II Simplified Addendum Version 1.02

Figure 3-3 : Point to Point Topology (Supporting 2L-HD Mode)

The default direction of D0 Lane is downstream, and D1 is upstream. If Host decides to send data to Device in 2L-HD mode, D1 Lane changes downstream temporarily (Figure 3-4 (a)). Similarly if Host decides to get data from Device in 2L-HD mode, D0 changes upstream (Figure 3-4 (b)). As a result, all Ports for data Lanes are necessary to have both functions of Tx and Rx.

Figure 3-4 : Direction Changing in 2L-HD Mode

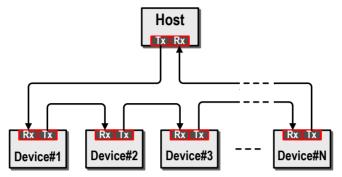

#### 3.2.2 Multi-device Connection

In order that Host can control or communicate with multiple Devices, UHS-II provides Multi-device connection. There are two types of topologies to realize Multi-device connection, one is Ring connection and the other is Hub connection. Ring connection is introduced to realize a cost effective topology that minimizes the total number of PHY in the embedded system. And Hub connection is introduced to realize more flexible topology compared to Ring, in terms of capability of hot insertion and removal. Note that RCLK shall be distributed individually to removable Devices, and not only UHS-II interface but also Legacy SD interface shall be connected to removable Devices.

#### 3.2.2.1 Ring Connection

Figure 3-5 illustrates an example of Ring connection. Connection rule of data Lanes is as follows. (Note that 2L-HD mode is not available in Ring connection in UHS-II Addendum Version 1.00.)

Figure 3-5 : Example of Ring Connection

- (1) D0.Tx of Host is connected to D0.Rx of Device#1

- (2) D1.Tx of Device#1 is connected to D0.Rx of Device#2, and this operation is repeated.

- (3) D1.Tx of Device#N (final Device) is connected to D1.Rx of Host, and Ring connection completes.

Examples of RCLK distribution method are illustrated in Figure 3-6.

Figure 3-6 : Examples of RCLK distribution method for Ring

Figure 3-6 (a) shows a multiple point to point method which uses a separate RCLK driver (RCLK.Tx) for each Device. With this method, Host needs to have at least the same number of RCLK.Tx Ports as the number of connecting Devices. If Host has only one RCLK.Tx Port, multi-drop method can be applied to connect multiple Devices (Figure 3-6 (b)). With this method, RCLK bus is terminated externally or at the final receiver. In addition this method requires careful signal integrity design.

Note that Device has only one RCLK.Rx Port even in the case of Figure 3-6 (b).

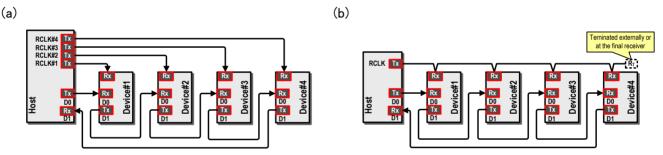

#### 3.2.2.2 Hub Connection

Figure 3-7 illustrates an example of Hub connection.

Hub shall have one Device PHY for Host connection and plural number of Host PHYs for Device connection. Hub also has functions such as transmitting signals to all connected Devices simultaneously, or selecting a packet destination according to its content.

#### **UHS-II Simplified Addendum Version 1.02**

Figure 3-7 : Example of Hub Connection

Note that from Device point of view behavior does not depend on UHS-II topology. Hub specification is not described in this document.

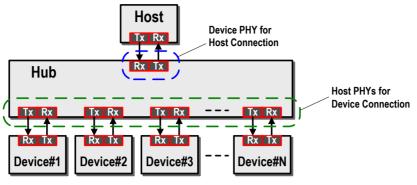

#### 3.3 Layering

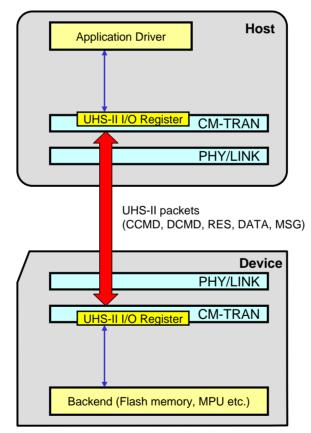

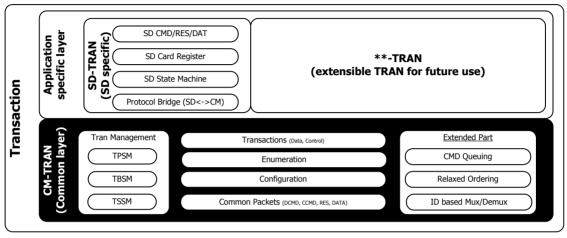

Figure 3-8 shows the overview of UHS-II interface layer structure.

Figure 3-8 : Layering Overview

Basically, UHS-II interface consists of four layers described below.

- **Mechanical layer** defines mechanical specification such as card form factor, connector pins and so on.

- **Physical layer (denoted by PHY)** defines electrical specification such as signaling architecture, and handle bit or symbol encoding and decoding.

- Link layer (denoted by LINK) is responsible for Link management including PHY initialization, and data integrity (packet framing / de-framing and CRC generation / checking). It is also in charge of power management and flow control.

- **Transaction layer (denoted by TRAN)** is responsible for protocol-base management including packet generation and analysis, command-response handshake, and so on.

TRAN is split into sub layers, one is a common layer called CM-TRAN and the other is an application specific layer. CM-TRAN is responsible for Basic IO or Memory transaction and control. The application specific layer bridges CM-TRAN and upper application layer in order to keep compatibility. SD-TRAN is one of the application specific layers and bridges CM-TRAN and Legacy SD applications or drivers. In this specification, SD-TRAN is also described. Other application specific layers can be defined in the future.

### 3.4 UHS-II Transaction

#### 3.4.1 UHS-II Packet

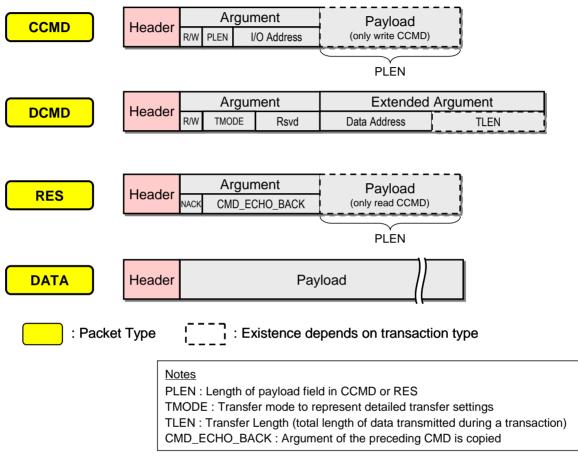

The following five packet types are defined for UHS-II TRAN. UHS-II Packet other than MSG is also called Transaction Layer Packet (TLP).

- Control command packet (denoted by CCMD) is a command without Data packet transaction. There are two categories of CCMD, one is P2P CCMD and the other is broadcast CCMD. Refer to Section 6.2.2.3 for the details of them.

- Data command packet (denoted by DCMD) is a command accompanied with Data packet.

- **Response packet (denoted by RES)** is a response that Device returns to Host after receiving CCMD or DCMD.

- Data packet (denoted by DATA) is for transmitting data payload between Host and Device.

- Message packet (denoted by MSG) is for transmitting short information. Only MSG is generated or analyzed in LINK.

Basically, UHS-II packet consists the following three parts, Header, Argument, and Payload. The Header part is common for all types of packet.

TLP is basically packetized based on information provided by TRAN and depacketized in LINK. Refer to packet format described in Section 6.2.2 or Section 7.2.1 for the details of the information.

Let initiator denote a Node (Host or Device) that newly creates a packet and transmits it. The following table indicates the initiator for each packet type.

| Packet Type | Initiator                                                 |  |

|-------------|-----------------------------------------------------------|--|

| CCMD/DCMD   | Host (regardless of P2P CMD or broadcast CMD)             |  |

| RES         | Device                                                    |  |

| DATA        | Node creating DATA packet                                 |  |

|             | (Host for write transaction, Device for read transaction) |  |

| MSG         | Node creating MSG packet                                  |  |

Table 3-1 : Definition of Initiator

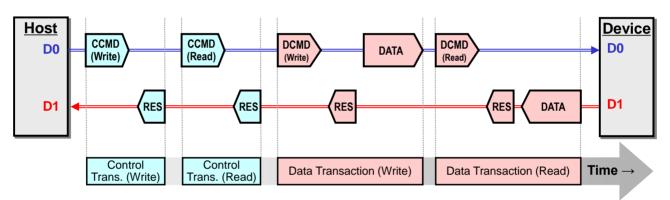

#### 3.4.2 Data Transaction

Length Unit Mode is defined to specify the unit of total data transfer length (TLEN) transmitted by Data packet (DATA). Length Unit Mode has the following two modes, one is a Block Mode and the other is a Byte Mode. Note that these modes can be set as a parameter of DCMD.

- **Block Mode:** TLEN is specified by a unit of Block Length, which is a payload length for one block. Block Length is finally determined through Configuration (refer to Section 0 and 6.2.9) or settings in the application specific layers.

- Byte Mode; TLEN is specified by a unit of byte. TLEN shall be less than or equal to Block Length.

Also refer to Section 5.2.6 about a data framing rule of above two modes. In addition, at most one data transaction can be executed in UHS-II Addendum Version 1.00.

#### 3.4.3 CM-TRAN

As described in Figure 3-8, UHS-II transaction layer is split into common layer (CM-TRAN) and application specific layer (SD-TRAN in case of UHS-II Card).

CM-TRAN specifies the common protocol suitable for UHS-II PHY and LINK (UHS-II native protocol). CM-TRAN generates UHS-II packets and sends them in the transmitter side according to the UHS-II I/O Register, or analyzes received packets in the receiver side. UHS-II I/O register is accessed by the Application Driver (Host) or Backend (Device).

Figure 3-9 : Basic UHS-II Transaction

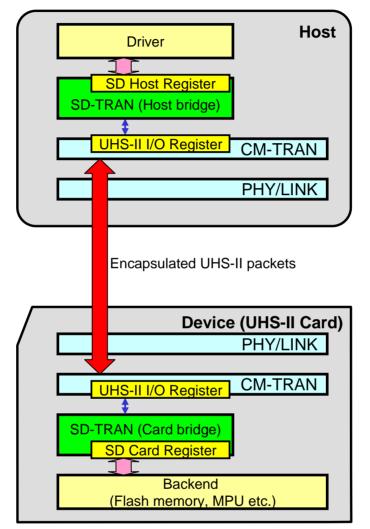

#### **3.4.4 SD-TRAN**

SD-TRAN bridges UHS-II interface (CM-TRAN) and Legacy SD IPs or software. SD-TRAN analyzes SD Host/Device Register and sets parameters to UHS-II I/O Register. In this case, CM-TRAN generates UHS-II packets which encapsulate Legacy SD command, response or data. Moreover, when CM-TRAN receives the encapsulated packets, CM-TRAN analyzes it and notifies to SD-TRAN.

Figure 3-10 : UHS-II Transaction by SD-TRAN

#### 3.4.5 Aborting Transaction

In UHS-II, TRANS\_ABORT CCMD is introduced as following purposes.

- Terminating data transmission in UHS-II native protocol. (Note that the encapsulated CMD12 shall be used instead of TRANS\_ABORT if SD-TRAN is implemented.)

- Aborting the outstanding transaction when timeout is detected.

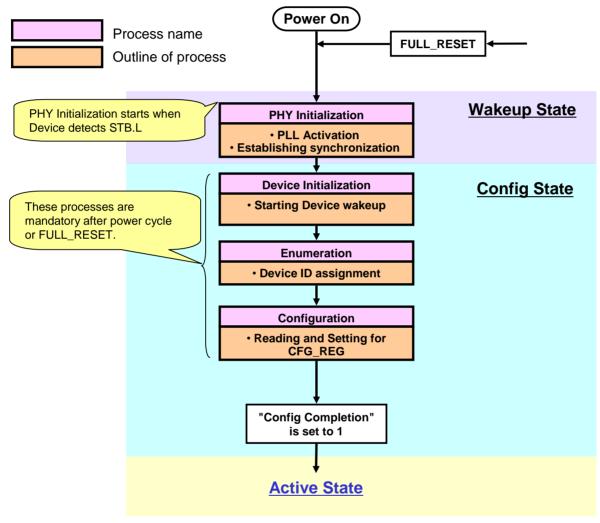

#### 3.5 UHS-II Initialization Outline

Host shall execute UHS-II Initialization flow as described in Section 3.5.1 (in case of without Boot Code Loading) or in Section 3.5.2 (in case of with Boot Code Loading). If Host violates those rules, Device operation is not guaranteed.

#### 3.5.1 UHS-II Initialization Flow without Boot Code Loading

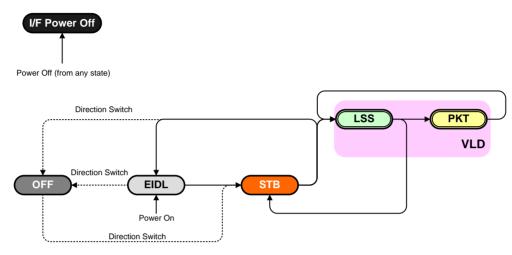

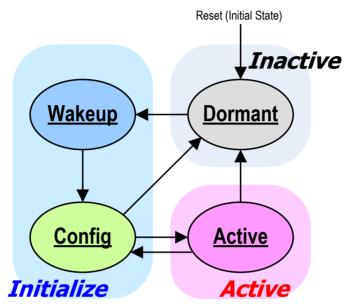

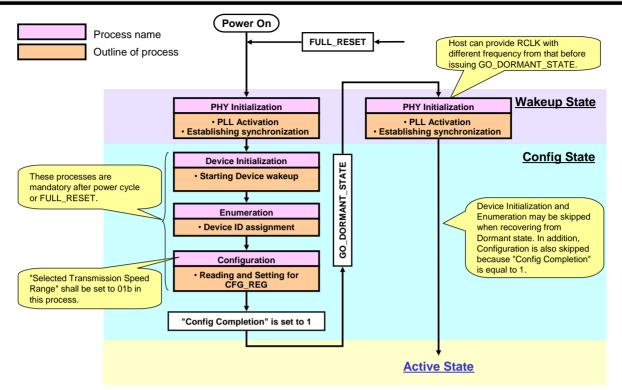

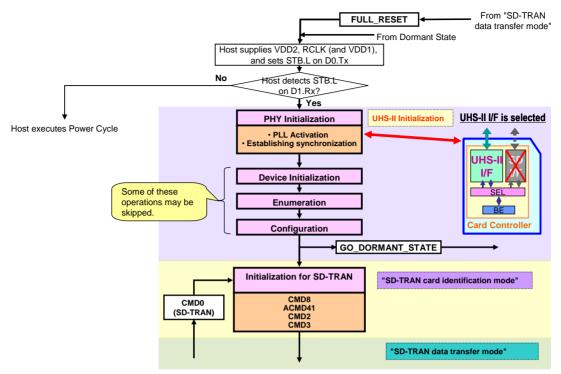

Figure 3-11 shows a UHS-II Initialization flow after I/F power cycle or issuing FULL\_RESET command (refer to Table 6-20 for more details). Details of state transition are defined in Section 5.2.9.

Figure 3-11 : UHS-II Initialization Flow

After I/F power cycle or FULL\_RESET, PHY Initialization process is started by Host's providing RCLK and STB.L.

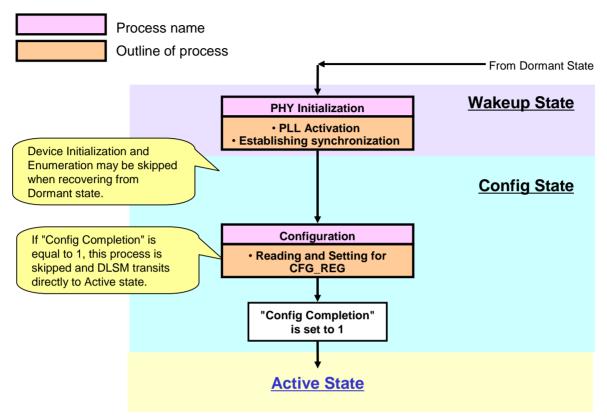

After finishing PHY Initialization, the state transits to Config State and the following three processes take place.

- **Device Initialization:** This process is executed by DEVICE\_INIT CCMD and makes whole components in Device activated. Refer to Section 6.2.6 for more details.

- Enumeration: This process is executed by ENUMERATE CCMD and assigns Node IDs for each

Device uniquely. Refer to Section 0 for more details.

• **Configuration:** This process is for determination of parameters for transaction among Host and Devices. First Host reads capabilities or properties from Configuration Register (CFG\_REG) of Devices, then determines the parameters for transaction, and finally writes the parameters to the register. Refer to Section 0 and 6.2.9 for more details.

If "Config Completion" flag defined in CFG\_REG is set to 1 successfully during Configuration process, the state transits to Active State.

Before completing Device Initialization it shall not operate and not transmit RES or broadcast CCMD when Device receives CMD other than DEVICE\_INIT CCMD.

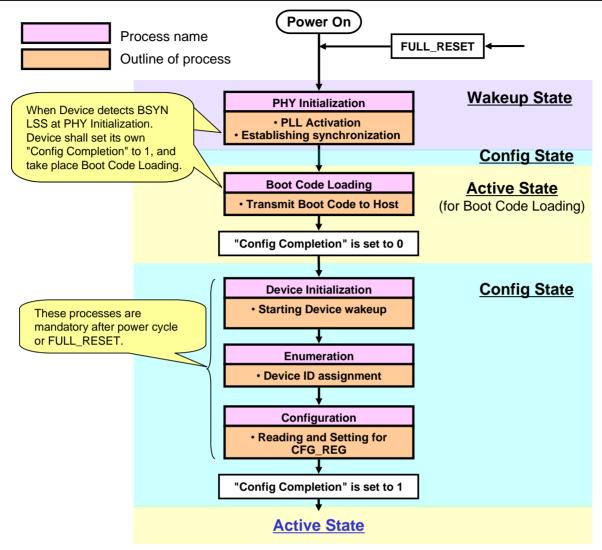

#### 3.5.2 UHS-II Initialization Flow with Boot Code Loading

It is possible for Host to load its Boot Code from one of connected Device, called Boot Device. Boot Device is optional in embedded system. It is required for Host to read the Boot Code as soon as possible.

Needless to say, Boot Device and Host are possible to transmit or receive Boot Code. In addition, considering the Ring connection, all other Devices also have functionality to bypass Boot Code and its related packets.

In this Section, the specification of loading Boot Code is described when the system includes Boot Device. This function is called "Boot Code Loading". Figure 3-12 shows UHS-II Initialization flow when Boot Code Loading is executed.

#### UHS-II Simplified Addendum Version 1.02

Figure 3-12 : UHS-II Initialization Flow When Boot Code Loading Is Executed

Different from Figure 3-11, Host transmits not SYN LSS but BSYN LSS in order to establish synchronization. At that time, all Devices shall set their own "Config Completion" to 1.

After finishing PHY Initialization, DLSM normally transits to Config state, but as "Config Completion" is equal to 1, DLSM immediately transits to Active state in order to execute Boot Code Loading.

After finishing Boot Code Loading, Host shall set "Config Completion" to 0 for all Devices before DEVICE\_INIT CCMD. Device shall accept the Broadcast Write CCMD for setting "Config Completion" to 0 even before receiving DEVICE\_INIT CCMD. Then DLSM transits to Config state. The rest of flow is same as Figure 3-11.

# 4. Physical Layer Specification

The details of UHS-II Physical layer such as signaling architecture electrical specification and handle bit or symbol encoding and decoding are described in this chapter.

The UHS-II standard is targeted for mobile, portable applications and home applications. It shall be compatible to legacy SD Cards. It provides enhanced data rate, while maintaining low power and low EMI. It is recommended for short cable length, typically below 20cm.

This UHS-II specification is defined for Card and also for Embedded Device. In this specification, "Device" means both Card and Embedded Device. If some specification items or descriptions are only for Card, "Card" is used. If some specification items or descriptions are only for Embedded Device, "Embedded Device" is used.

The key features of Physical Layer are defined as follows:

- Differential low voltage Signaling with DC coupling

- Flexibility of transmission rates

- Low Frequency Reference Clock (RCLK)

- Two types of duplex mode: FD mode (mandatory), 2L-HD mode (optional)

- Additional pins for High-Speed Differential transmission

- 8b/10b coding

- Enhanced power saving modes

#### 4.1 Physical Layer Overview

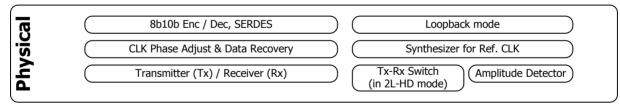

Physical layer consists of the following functions:

- Differential Transmitter(Tx) and Receiver(Rx)

- CLK phase adjustment and Data recovery

- Serializer and De-serializer (SERDES)

- 8b/10b encoding and 10b/8b decoding

- Amplitude Detection

- Synthesizer for Reference CLK

Figure 4-1: Physical Layer Overview

#### 4.2 Physical Layer Interface Architecture

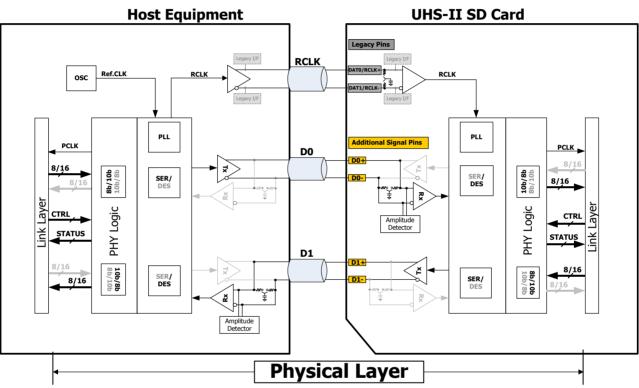

Figure 4-2 illustrates an example of the interface architecture of physical layer in case of point to point connection between Host and Card. The UHS-II interface utilizes transmission Lines (including socket and pins) and terminations which are meant to keep the impedance matching for high speed transmission. UHS-II interface introduces the additional pins for high speed data transmission.

UHS-II interface has continuous variable data rate from 39MB/sec to 156MB/sec as effective data rate. Device shall cover the whole range.

UHS-II has two data Lanes. As default, one Lane (D0) is used for downstream (from Host to Device), and another Lane (D1) is used for upstream (from Device to Host). Both data Lanes may be used for downstream Lanes or upstream Lanes at the same time by activating the 2L-HD mode (optional). The transmitted data is encoded by 8b/10b encoder.

The Differential Clock (RCLK) may be tuned in the range of 26MHz to 52MHz. Regarding Card, RCLK is sent through the legacy SD transmission lines DAT0, DAT1 and corresponding Card pins.

Amplitude Detectors, which detect the Lane's electrical level, are equipped to Host side of D1 Lane (optional) and Device side of D0 Lane (mandatory). Amplitude Detectors make the I/O circuits, such as receiver, to wake up when transmission is resumed at the Lane after Dormant state.

Note 1: All function blocks and connection lines used in 2L-HD mode are colored by gray.

Note 2: I/O circuits of Legacy SD Interface, which are not used in UHS-II, are shown by dash-line and filled with light gray.

Note 3: RCLK termination of each device shall be switchable.

#### Figure 4-2: Physical Layer Interface Architecture

#### 4.2.1 Lane Definition

Host and Device are connected by 3 differential Lanes with DC coupling:

#### • High speed data Lanes (D0, D1):

D0 is used for downstream (from Host to Device), thus WRITE data and command are transferred from Host to Device on this Lane. However, when enabling the optional 2L-HD mode, it is possible to use D0 Lane as upstream (from Device to Host).

D1 is used for upstream, thus READ data and response are transferred from Device to Host on this Lane. However, when enabling the optional 2L-HD mode, it is possible to use D1 Lane as downstream.

D0 and D1 Lanes are used for differential transmission between Host and Device which are dedicated to UHS-II interface only, and are separate for signals of legacy SD interface. The D0

and D1 signals are encoded by 8b/10b code before transmission, and decoded by 10b/8b after receiving, as described in Section 4.5.

#### • Reference clock Lane (RCLK):

RCLK is transmitted from Host to Device. Whenever Host output a RCLK to the UHS-II Device, the RCLK signal frequency and phase should be stable. The RCLK shall not be stopped and its frequency shall not be changed during UHS-II transmission, even within the same range. (Refer to Section 4.2.2 for the Range definition and Section 6.2.3 for frequency change procedure).

The RCLK frequency is lower than lowest data rate. Therefore, the Device shall generate high frequency clock or multi-phase clocks internally for sampling the high-speed data. The RCLK frequency is in the range of 26MHz to 52MHz; Data rate is from 390Mbps to 1.56Gbps per Lane (Refer detail in Section 4.2.2).

Regarding Card, RCLK is sent through DAT0 and DAT1 lines of legacy SD interface. Thus, RCLK does not require additional pins. Card RCLK receiver shall be tolerant to single ended voltage range of 0V to 3.6V DC.

For power save purposes, when no data is transferred each Lane may enter EIDL state individually, or all Lanes including RCLK Lane may enter EIDL state concurrently, which is called Dormant state. During those states and mode, an Amplitude Detector of each D0, D1 Lane is active, monitoring the Line voltage and flagging wakeup notice. After detecting the wakeup notice, the detector activates PHY circuits of own port.

#### 4.2.2 Range Definition for Data Rate

In UHS-II, RCLK frequency is in the range 26MHz to 52MHz and Data rate is 390Mbps to 1.56Gbps per Lane accordingly. This range is divided to two ranges for the ease of PLL design as shown in Table 4-1. Initialization of UHS-II interface after power down shall be done with the Range A.

Device PLL acquisition time shall be at most 2ms. But only the first PLL acquisition time after power up, PLL of Host and Device shall finish locking less than 100ms. This is Tactivate.

|         | RCLK Frequency  | Data Rate/channel   | Ratio<br>(Data rate / RCLK<br>Frequency) |

|---------|-----------------|---------------------|------------------------------------------|

| Range A | 26MHz to 52 MHz | 390Mbps to 780Mbps  | x 15                                     |

| Range B |                 | 780Mbps to 1.56Gbps | x 30                                     |

Note: Even if supporting SSC, the minimum RCLK frequency shall not be lower than 26MHz.

#### Table 4-1: Range Definition for Data Rate

#### 4.2.3 Power Supply Connections

Two power supply connections are needed for UHS-II interface, named VDD1 and VDD2, for powering the Device by the Host.

VDD1 is dedicated for powering the legacy SD interface, logic and the memory devices in the Device VDD2 is used for powering UHS-II interface. It should power the PHY and upper layers logic.

GND node is common to all the devices and all the circuits. It is also used as reference for the UHS-II signaling levels, thus it is recommended that both Host and Device design for minimal DC variation and AC noise on this node.

Section 4.2.4 to Section 4.2.7 is a blank in the Simplified Addendum.

# 4.3 Electrical Specification

Section 4.3.1 to Section 4.3.2 is a blank in the Simplified Addendum.

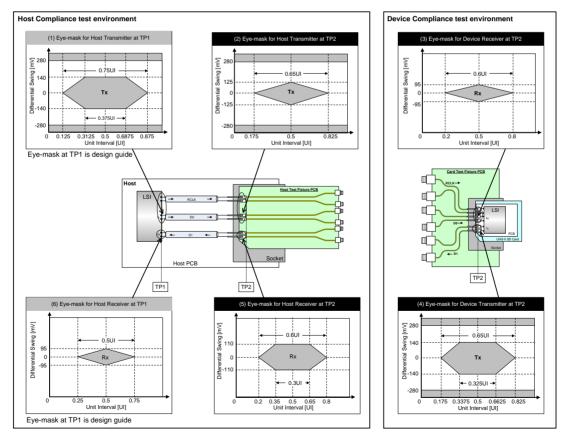

#### 4.3.3 Eye-mask Template

The eye-mask templates are the graphical representation of the limit for the voltage and jitter for the differential signals. The eye-mask templates of UHS-II are shown in Figure 4-6. The horizontal margin of eye-mask template is calculated as 1 UI -  $T_J$ .

For the transmitters of Host and Device, when transmitting differential signal, these signals including over/under-shoot shall remain in the white area of each Eye-mask template (Tx) in Figure 4-6 at any time except in EIDL state.

For the receivers of Host and Device, when receiving the differential signals that have the eye-opening shown in eye-templates (Rx) in Figure 4-6, receivers shall receive these signals correctly.

The eye mask templates specified in Figure 4-6 refers to measurements at standard measurement conditions and BER of 1E-12. The standard measurement conditions are described in UHS-II PHY Test Guideline document.

Note: The Host and Device are tested separately at "ideal" compliance environment, while in real system Host and Device are connected together, so there will be some mutual effects because of this connection. The margin between (2) to (3) Eye-masks and (4) Eye-mask to (5) Eye-mask are taken because of that. The following elements are covered by this margin:

- A. Power delivery noise,

- B. Internal Device Xtalk due to other internal activity

**Figure 4-6: Eye-mask Templates** Notes of Figure 4-6 is a blank in the Simplified Addendum.

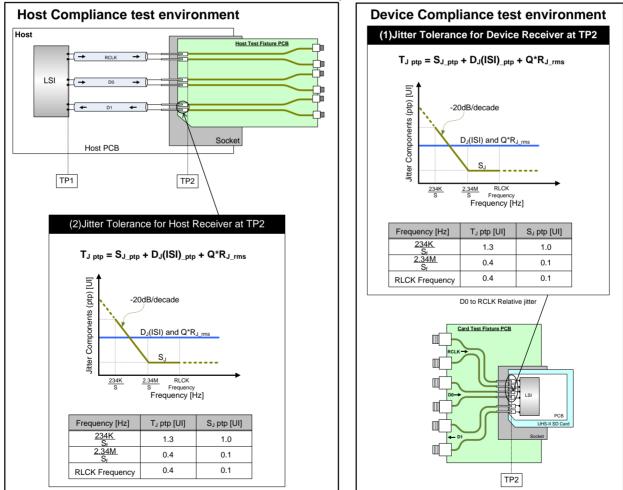

#### 4.3.4 Jitter

The relation between eye-opening and total jitter is defined by Eye Opening =  $1UI-T_J$ . The more jitter, the less eye-opening. Thus, for ensuring the interconnection between Host and Device, jitter specification shall be adhered for each differential Lane: RCLK, D0 and D1.

Total Jitter  $T_J$  consists of two jitter components: deterministic peak to peak jitter  $D_J$  and random root mean square jitter  $R_{J-rms}$ .

Total Jitter  $T_J$  is calculated by the following equation:

$$T_J = D_J + Q \cdot R_{J_rms}$$

Where, Q factor is related to Bit error rate (BER). In UHS-II, BER performance of PHY shall be achieved by  $10^{-12}$ , when Q is 14.1.

The  $D_J$  contains two elements  $D_J(ISI)$  which is the deterministic jitter caused by ISI and  $S_J$  which is a sinusoidal jitter component.

Test pattern, jitter element budgeting and jitter injection method is specified in UHS-II PHY Test Guideline document.

#### Section 4.3.4.1 to Section 4.3.4.2 is a blank in the Simplified Addendum.

**Figure 4-7: Jitter Tolerance Specification** Notes of Figure 4-7 is a blank in the Simplified Addendum.

#### 4.3.5 Return Loss

The mismatch and unbalance of impedance between the components which form transmission Line causes the signal reflection. Signal reflection contributes to the degradation of signal integrity and EMI.

The return loss limits (differential return loss, common-mode return loss and common-to-differential return loss) are defined in UHS-II specification for keeping signal integrity and EMI mitigation. Both transmitter and receiver shall comply with the return loss specification. When 2L-HD mode is supported, each port is bi-directional, thus return loss specification are applied for transmitter and receiver respectively.

The return loss is defined as the ratio of reflected power to incident power, and measured by using Test fixtures (Refer to Appendix C). The characteristic impedances of the Test Fixtures (mean differential impedance and common-mode impedance) are reference values for the return loss measurement. For Return Loss testing, De-embedding of the test fixture should be performed.

The detailed measurement method is described in UHS-II PHY Test Guideline document.

Following of Section 4.3.5 is a blank in the Simplified Addendum.

Section 4.3.6 to Section 4.3.7 is a blank in the Simplified Addendum.

Section 4.4 to Section 4.5 is a blank in the Simplified Addendum.

#### 4.6 Loopback Mode

The PHY block in the Device and Host shall have loopback path that is needed for testability purposes, and the loopback path is also used for Devices in order to perform data bypassing in ring topology. It is expected that loopback path will have the same clocking scheme as Tx and Rx lanes in FD mode, for both forward and backward loopback.

The loopback causes the data that is received at the serial input of a Lane to transmit at the serial output of another Lane after recovery. The loopback is done from the output of the de-serializer in the receiver path, to the input of the serializer of the transmitter path, by dedicated 10 bit multiplexer in the transmitter block. This loopback enables testing the PHY with any symbols including patterns which are illegal for 10b/8b decoding.

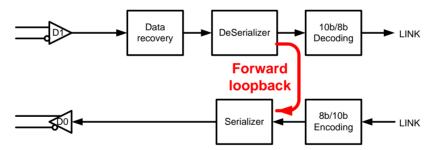

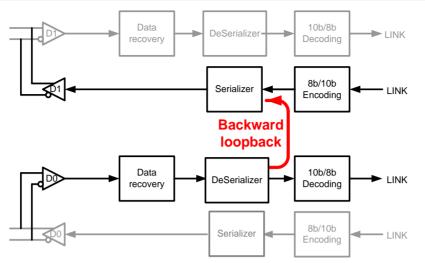

In normal condition, the loopback path in the PHY of the Host is done from the D1 receiver to the D0 transmitter, as presented in Figure 4-15. This path is named "forward loopback". For testing the other direction, which test D0 as receiver and D1 as transmitter, which are used in 2L-HD mode, there is a need for backward loopback path, as shown in Figure 4-16.

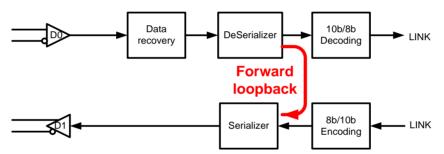

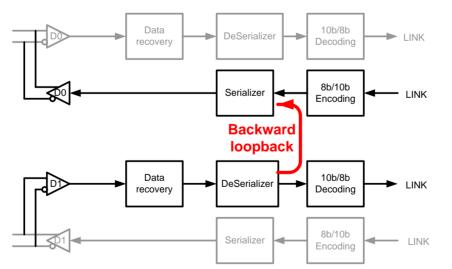

In normal condition, the loopback path in the PHY of the Device is done from the D0 receiver to the D1 transmitter, as presented in Figure 4-17. This path is named "forward loopback". For testing the other direction, which test D1 as receiver and D0 as transmitter, which are used in 2L-HD mode, there is a need for backward loopback path, as shown in Figure 4-18.

The loopback modes are controlled by the LINK layer while in normal operation, while in Test mode loopback may also be controlled internally in the PHY. Each PHY vendor may specify additional loopback modes, but it is beyond the mandatory requirements of the standard.

Figure 4-15: Location of Forward Loopback in PHY of the Host

Figure 4-16: Location of Backward Loopback in PHY of the Host

Figure 4-17: Location of Forward Loopback in PHY of the Device

Figure 4-18: Location of Backward Loopback in PHY of the Device

#### 4.7 PHY Test Mode

For the Compliance test of UHS-II PHY, Re-Sync state and following method are defined to UHS-II PHY in order to configure PHY for the specific test condition.

In PHY Test mode, Dormant state and Re-Sync state are used in case of changing PLL multiplier.

Dormant state used in PHY Test mode is the same state as in UHS-II normal operation, which is applied to the Rx which has Amplitude Detector (for example, Device D0.Rx), Therefore in the Dormant state during PHY Test mode, all PHY circuitry are powered off except Amplitude Detector. When exiting Dormant state, Amplitude Detector is used to detect STB.L.

Re-Sync state is applied to the Rx which has no Amplitude Detector (for example, Device D1.Rx). In the Re-Sync state PHY circuitry keeps power on (except for PLL while changing its multiplier) because Rx having no Amplitude Detector shall be able to receive symbols from Test equipment.

The difference between Dormant state and Re-Sync state is whether PHY is powered off or still powered on. Exiting Dormant state and Re-Sync state take the same sequences (Sequence to exit Dormant or Re-Sync; refer to Fig 4-19). When exiting these states, re-synchronization of CDR is performed.

Items to be configured in Test mode are as follows.

- Disconnect and Normal (Non-Disconnect) mode

- Disconnect mode:

Device and Host keep current test mode for any input levels.

That means Device and Host do not enter Dormant state even if the connection change happens between the Device/Host and test equipment. It is possible to exit Disconnect mode by using Power cycle, or transfer to Normal mode by using "Sequence to Set Test Mode".

- Normal (Non-Disconnect) mode: This mode is capable to enter the Dormant state. This mode is useful to perform multiple test items automatically.

- Loop Back Direction

- Forward Loopback:

Default loopback direction for all Devices and Hosts.

- Backward Loopback:

Device and Host which support 2L-HD mode support Backward Loopback.

For Detailed Definition of Loopback modes, refer to Section 4.6 Loop Back mode.

#### Notes:

- 1. To enter Backward Loopback test mode, the sequence to set Test Mode (refer to Figure 4-19) shall be provided on Device D0 Rx and Host D1 Rx.

- 2. To enter Forward Loopback test mode retrieved from Backward Loopback test mode, the sequence to set Test Mode (refer to Figure 4-19) shall be provided on Device D1 Rx and Host D0 Rx.

- 3. Dormant state shall be used on Device D0 Rx (Forward Loopback) for testing an Amplitude Detector.

- 4. Which state Dormant or Re-sync should be used is dependent on implementation of Amplitude Detector especially on Device D1 Rx (Backward Loopback), Host D0 Rx (Backward Loopback) and Host D1 Rx (Forward Loopback).

- 5. Device and Host may transmit a few broken symbols instead of COM+SYN symbols expected, on switching Loopback direction.

- PLL Multiplier factor

PLL Multiplier factor may be set by the test mode entry method without setting configuration Register. Change of PLL Multiplier is effective only when exiting Dormant or Re-Sync state.

• <u>Future Test Mode Expandability</u> Additional vendor specific Test Modes may be defined.

### UHS-II Simplified Addendum Version 1.02

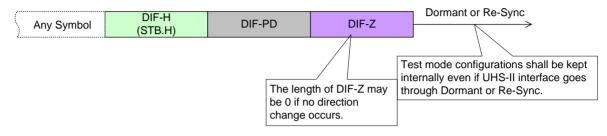

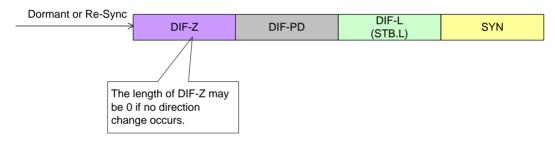

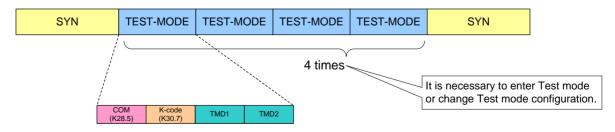

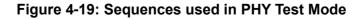

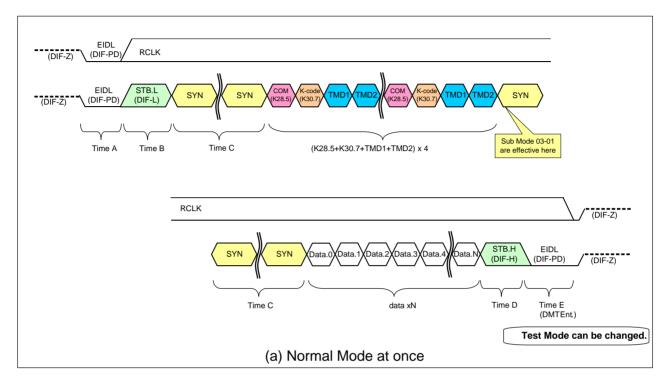

### 4.7.1 The Sequences used in PHY Test Mode

Figure 4-19 shows the sequences used in PHY Test Mode. Test mode configuration is done by setting the TMD1 and TMD2 in the symbol named "TEST-MODE" (which is constructed by COM (K28.5) + K-code (K30.7) + TMD1 + TMD2 as described in Figure 4-19). To avoid entering a test mode by mistake, TEST-MODE symbol is sent 4 times continuously.

# Sequence to Enter Dormant or Re-Sync

- When necessary to change PLL multiplier, this sequence is used

# Sequence to Exit Dormant or Re-Sync

- When direction is switched, started by this sequence.

- When necessary to change PLL multiplier, this sequence is used

# Sequence to Set Test Mode

- Before setting Test-Modes, re-synchronization should be performed by through Dormant or Re-Sync state. (Not necessary for every test mode setting.)

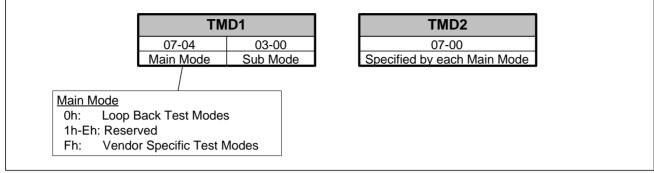

## 4.7.2 Definition of TMD1 and TMD2

The structure of TMD1 and TMD2 are defined as follows and in Figure 4-20. Device maintains setting of TMD1 and TMD2 during PHY test mode until Host changes setting of TMD1 and TMD2, even if going through Dormant or Re-Sync mode.

### 4.7.2.1 TMD1

TMD1 is used for configuring Main mode and Sub mode.

Upper 4-bit is used to assign Main Mode:

- **0h** : assigned for Loop Back Test Modes

- **Fh** : assigned for vendor specific test modes (Vendor may define TMD1 and TMD2 to control vendor specific test modes)

Lower 4-bit is used to assign Sub Mode:

- "Timing" (Sub Mode 00): determines the timing when Sub-Mode 03-01 is effective.

- "Disconnect"(Sub Mode 01): determines whether Disconnected mode or Normal (Non-Disconnect mode).

### 4.7.2.2 TMD2

TMD2 is specified by each Main Mode.

"Loop Back Direction"(07): determines whether Forward Loop back or Backward Loop back. When this bit is changed, the change of Loop Back Direction is done immediately. Everytime Loopback direction is changed, both D0 and D1 are set to input at first in order to re-connect Test tool.

After re-connecting Test tool to Device/Host:

<In case Loop Back Direction bit is changed 0 to 1>

- After Device detects SYN from D1, D0 is enabled as output, and then the change of Loopback direction is done.

- After Host detects SYN from D0, D1 is enabled as output, and then the change of Loopback direction is done.

<In case Loop Back Direction bit is changed 1 to 0>

- After Device detects SYN from D0, D1 is enabled as output, and then the change of Loopback direction is done.

- After Host detects SYN from D1, D0 is enabled as output, and then the change of Loopback direction is done.

- "SSCE"(06): controls Host SSC On/Off if Host supports SSC function. This bit is not effective to Device.

- "PLL Multiplier factor"(02-00): determines PLL Multiplier (x15 or x30). The actual change of PLL Multiplier is done after exiting Dormant or Re-Sync state.

(a) General Definition

### (b) TMD1 and TMD2 Definition in Loop Back Test Mode

Note: Symbols are described in 8-bit domain for the convenience of explanation. Actual symbols to enter and exit test mode are transferred from test equipment after 8b/10b encoding.

### Figure 4-20: Structure of TMD1 and TMD2

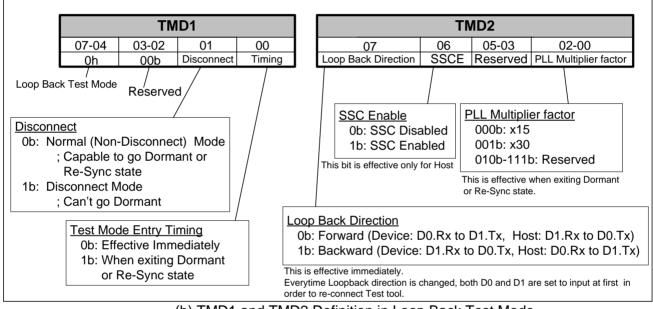

### 4.7.3 Test Modes

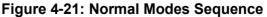

Parameters for entering each Test mode are described as follows. The sequences for entering each test mode are shown in Figure 4-21 and Figure 4-22.

### TMD1 Modes:

• 00h: Normal Mode At Once

Setting in Sub Modes 03-01(Normal Mode) is effective immediately. After entering a test mode, it is possible to go back to Dormant state.

- O1h: <u>Normal Mode Through Dormant state</u> Setting in Sub Modes 03-01(Normal Mode) is effective when exiting Dormant state. After entering a test mode, it is possible to go back to Dormant state.

- O2h: Disconnect Mode At Once

Setting in Sub Modes 03-01 (Disconnect Mode) is effective immediately.

After entering a test mode, the Device cannot go Dormant state.

- O3h: Disconnect Mode Through Dormant state

Setting in Sub Modes 03-01 (Disconnect Mode) is effective when exiting Dormant state.

After entering a test mode, the Device cannot go Dormant state.

### TMD2 Modes:

PLL Multiplier (Bit 02-00)

- 000b: x15

- 001b:x30

- 010b-111b: Reserved

Change of this field is effective when exiting Dormant or Re-Sync state. Clock frequency may be changed only during Dormant or Re-Sync state.

Loop Back Direction (Bit 07)

- 0b: Forward Loop Back (means from D0.Rx to D1.Tx)

- 1b: Backward Loop Back (means from D1.Rx to D0.Tx)

When this bit is changed, both D0 and D1 are set to input mode immediately.

### UHS-II Simplified Addendum Version 1.02

Time A= EIDL Length= After Power up 100ms (min.) (Manual Start) and after that 200us.Time B= Teidl\_stb= 200us(min.)Time C= Tactivate= After Power up 100ms (min.) and after that 2ms (min.)Time D= T\_EIDL\_ENTRY= 4SI (min.) PHY Spec. defines as fixed but test mode defines as min.

### UHS-II Simplified Addendum Version 1.02

Figure 4-22: Disconnect Mode Sequence

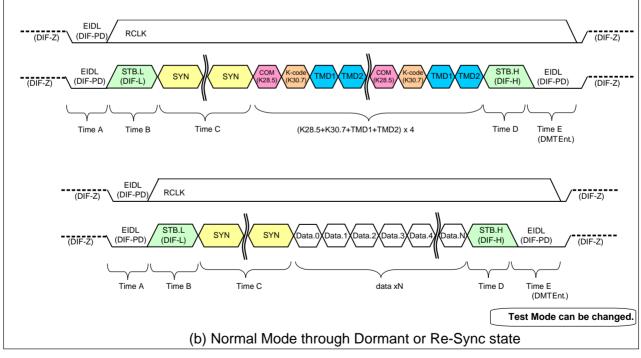

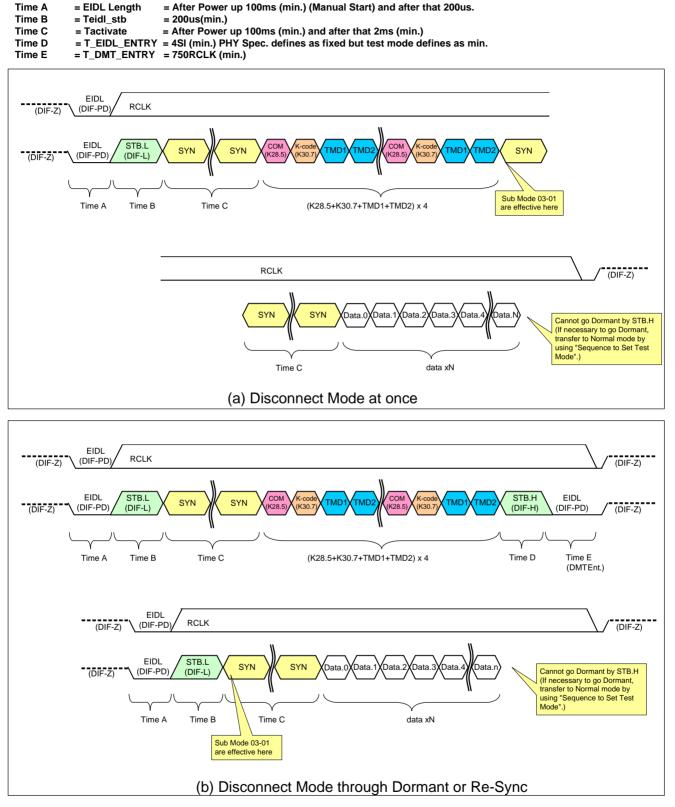

### 4.7.4 An Example Procedure

An example procedure for entering test mode is shown in Figure 4-23. This procedure is about Backward Loop Back test under the condition that PLL Multiplier is x30.

Figure 4-23: An Example Procedure (Backward Loop Back Test with PLL Multiplier is x30)

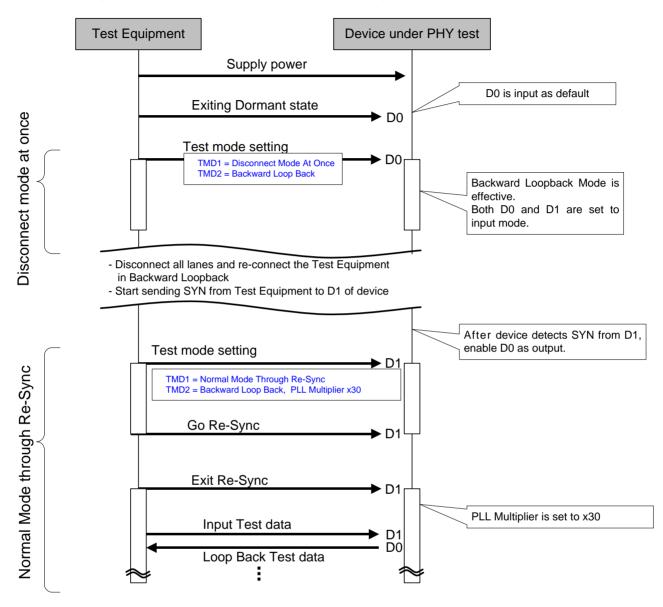

### 4.7.5 Test Mode for Host

Host shall have "Slave Mode" and enter this mode for Host PHY test. The Slave Mode is correspondent to Dormant state of a Device. The method to enter the Slave Mode depends on Host implementation. Figure 4-24 shows the states regarding Host PHY Test.

Figure 4-24: States Regarding Host PHY Test

In Slave Mode,

- Host watches D1 Line to detect the sequence for Test Mode entry.

- · Host continuously provides RCLK at any frequency selected by itself.

- Disable SSC when entering Slave Mode as a default.

When entering PHY test mode from Slave mode,

- PLL Multiplier may be changed by TMD2

- Backward Loop Back mode may be selected by TMD2

- SSC Enable may be changed by TMD2

When the Slave Mode and PHY Test Mode, test equipment may be connected to Host.

The following is recommended for Host:

• Disable all timeout detectors when the sequence for Test Mode entry is detected

Following of Chapter 4 is a blank in the Simplified Addendum.

# 5. Link Layer Specification

# 5.1 Link Layer Overview

Figure 5-1 shows the overview of Link Layer.

| ſ    | Link Management |                                                             |

|------|-----------------|-------------------------------------------------------------|

|      |                 | Flow Control                                                |

| -ink | DLSM            | In-band Link Message (MSG)                                  |

| -    |                 | Data Integrity (Framing & CRC) Direction Control (Optional) |

| l    | PLSM(D0/D1)     | LSS (SYN, LIDL, SOP, EOP,) PHY Initialization               |

Figure 5-1 : Link Layer Overview

Link Layer is in charge of controlling data flow and making management for LINK and PHY. The key features of Link Layer are defined as follows.

- PHY Initialization Control

- Data Integrity: Packet framing with SOP and EOP, CRC generation and checking.

- Flow Control: Fixed window flow control only for Data packet transfer.

- Direction Control: Duplex mode switching between FD mode and 2L-HD mode (Optional).

- **Power Management (PM):** Lane level power saving state (EIDL: Electrical Idle) Link level power saving state (Dormant)

- PHY and LINK error handling

- Packet Bypassing

# 5.2 Link Layer Protocol

## 5.2.1 Protocol Overview

Link Layer generates Link Symbol Set (LSS) to control PHY (synchronization, direction control, etc.), frames UHS-II packet (refer to Section 3.4.1 for more details) in terms of packet separation and data integrity. When Link accepts outgoing packets from upper layer (CM-TRAN), it generates CRC for each packet and the packet accompanied by its CRC is framed with SOP and EOP LSS. The framed UHS-II packets are transmitted through UHS-II bus via PHY. Each byte of original packet and CRC is encoded to 8b/10b Data symbol (D) in PHY. Refer to Chapter 4 for the 8b/10b encoding scheme.

# 5.2.2 Link Symbol Set (LSS)

Section 5.2.2 is a blank in the Simplified Addendum.

### 5.2.3 Header for UHS-II Packet

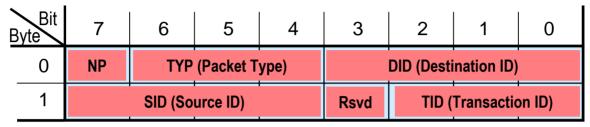

Figure 5-2 illustrates header structure for UHS-II packet that is compliant to UHS-II Addendum Version 1.00. First, Node ID whose range is from 0 to 15 denotes a value to identify the individual Hosts and Devices. Node ID = 0 is set aside for Host. For Devices, number 15 is set as the initial value for Node ID after I/F power cycle or FULL\_RESET, and one of numbers from 1 to 15 is assigned to each Device by Enumeration process described in Section 0. Note that Node ID of Boot Device is temporarily assigned for Boot Code Loading at first, then one of numbers from 1 to 15 is assigned by Enumeration.

Considering future extension, header format is allowed to be changed linked to LINK/TRAN Major Revision in CFG\_REG (refer to Table 6-9).

Figure 5-2 : Header Format

UHS-II Packet Header shall be composed of the following fields;

- NP (Native Packet): Indicator whether the packet follows native protocol or not

- 0: not native protocol (application specific protocol)

- 1: native protocol

- NP field in MSG shall be set to '1'. (MSG packet transaction is defined on native protocol.)

- TYP[2:0] (Packet Type): Packet type described in Table 5-3.

- DID[3:0] (Destination ID): Node ID of destination Device or Host.

- SID[3:0] (Source ID): Node ID of source Device or Host.

- TID[2:0] (Transaction ID): Identification number of outstanding transactions

- The TID field is defined in order to manage outstanding transactions for multiple command execution. (Details of multiple command execution will be defined in the future specification.)

- Rsvd (Reserved): Reserved bits. Initiator shall set them to '0', and receiver shall ignore them.

| TYP [2:0] | Packet Type | Description            | Note            |

|-----------|-------------|------------------------|-----------------|

| 000b      | CCMD        | Control Command packet | TLP             |

| 001b      | DCMD        | Data Command packet    | TLP             |

| 010b      | RES         | Response packet        | TLP             |

| 011b      | DATA        | Data payload packet    | TLP             |

| 111b      | MSG         | Message packet         | Handled in LINK |

| Others    | Reserved    | Reserved               |                 |

### Table 5-3 : Packet Type Encodings and Descriptions

DID and SID are used as routing information. If SID = DID, the packet is handled as broadcast. For UHS-II Addendum Version 1.00, broadcast packet is applicable only for CCMD. Details of broadcast CCMD are described in Section 6.2.2.3.

Basically, Host or Device processes a packet with the same DID as its own Node ID. In case of receiving a packet with different DID from own Node ID, Host or Device does not process it except broadcast packet and bypasses it to the next Host or Device on the bus. If Host or Device receives broadcast packet (SID = DID), it shall process even when DID is not equal to its own Node ID, and transmit to the next Host or Device.

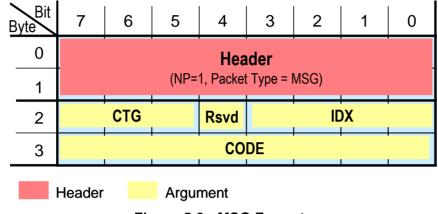

# 5.2.4 Message Packet (MSG)

### 5.2.4.1 Overview

Message Packet (MSG) is introduced to realize flow control, error or interrupt handling instead of hardwired signals.

Figure 5-3 illustrates a structure of MSG packet. Note that NP in Header shall be set to 1.

Figure 5-3 : MSG Format

- CTG[2:0] (Message Category): indicates category of MSG.

- Refer to Table 5-4 for more details.

- IDX[3:0] (Message Index): indicates message Index related to CTG. Refer to Table 5-4 for more details.

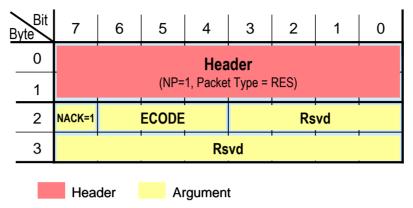

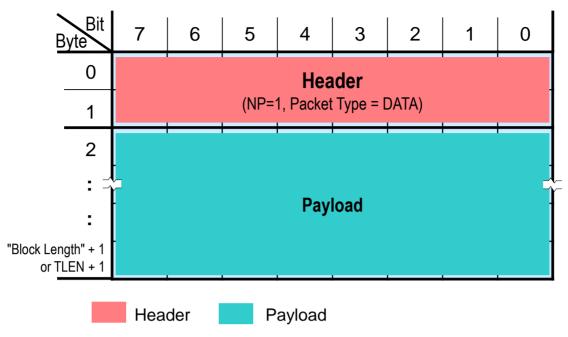

- CODE[7:0] (Message Code): indicates code to define message detail.